胡奇宇,陈益民,彭松

(广东工业大学 信息工程学院,广东 广州 510006)

摘要:基于0.18 μm CMOS标准工艺设计了一种低电压高性能运算放大器。阐述了具有负反馈的三支路基准电流源、带有正反馈环路增益提高的CMOS源极耦合差分输入级结构电路。基于频率补偿思想,提出一种新型频率补偿方法,能够有效提高运算放大器的系统性能。经版图后仿真表明:该运算放大器在1.2 V电源电压下具有109 dB的直流增益,259 MHz的增益带宽,相位裕度74°,功耗为0.82 mW,能够广泛应用到大多数电路中。

关键词:低电压;三支路基准电流源;正反馈环路;前馈补偿

中图分类号:TN432文献标识码:ADOI:10.19358/j.issn.1674 7720.2016.23.008

引用格式:胡奇宇,陈益民,彭松. 一种低电压高性能的运算放大器设计[J].微型机与应用,2016,35(23):28-30.

0引言

运算放大器在实际电子产品设计中是最基本的模块,随着电子产品不断地向便捷式方向发展,对它的电压要求越来越低,目前在提高低压运放的性能时,最值得关注的发展动向是对结构的改进[1]。本文在新的框架结构中引入亚阈值工作电路,使差分输入MOS对管工作于亚阈值区,电路工作在亚阈值状态时电流很小,以此降低功耗。对输入级差分对的负载采用交叉耦合带正反馈的结构,通过增大输入管的跨导来提高增益。频率补偿使用一种新的前馈技术取代传统零极点分离带密勒电容的补偿技术。

1运算放大器的电路实现

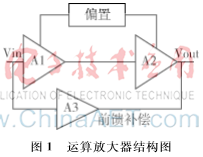

本文所设计的运放电路由偏置模块、两级放大模块、前馈补偿电路构成,如图1所示。其中偏置电路提供基准电流;两级放大模块是运放的核心电路;前馈模块为运放提供一定的增益及频率补偿,使系统稳定。

1.1三支路基准电流源

基准电流源是模拟集成电路中用来为其他电路提供高精度、低温度系数的电流源,是电路中必不可少的模块[2]。为了提高供给运放基准电流的电源抑制比(PSRR),使基准电流随VDD的变化较小,该设计采用三支路基准电流源结构。如图2所示。

其基准电路由MOS管M1~M6和电阻R构成。该电路在普通基准电流源的基础上增加一条由M5、M6构成的从电源到电阻R上端后到地的第三条支路,用于形成负反馈。工作原理:当电源电压正向增加时,ID5的A点电压升高,使得M2的漏端B处电压降低,在M1管的作用下,ID1的C点电压升高,同样M6作为共源级作用下,使得ID6的A点电压降低,形成负反馈回路。

为增强其负反馈系统的增益,M6源极与M2源极接在一起后接至产生电压差的电阻R上端,同样当电源电压波动正向增加时M5漏端A处电压升高,M5、M4管的VSG将会降低,ID5、ID4均减小,由电阻R两端电压VR=(ID5+ID4)×R得,电阻R上端电压降低很快,从而使M5漏端电压迅速下降,整个电路形成一个更快的负反馈,抑制了电源电压的变化对系统的影响。

为了使得到的镜像后的电流IREF的值更精确,在电路中需确保ID3=ID4,即M3与M4的各端电压要偏置一致。如图2所示,M5、M4、M3构成电流镜,M7M9为启动电路。通过调整M5的漏电流和M6的宽长比,使得VGS6与VGS2相等,由VD1=VD6=VS2+VGS6=VS2+VGS2=VD2得VD3=VD4,因M3、M4源端、栅端都与衬底直接相连,工作状态一样,所以得到:

工作在饱和区MOS管的源漏极电流表达式为:

设计中增加了MOS管的栅长,以便忽略沟道长度调制效应。上式中λVDS可以忽略。MOS管在临界饱和状态时源漏极电流表达式为:

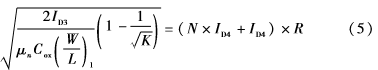

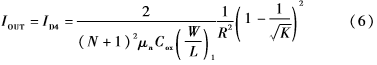

在电路中电阻R产生的源端电压差VR=(ID5+ID4)×R,初步设计第三支路M5、M6流过的电流为基准电流源的N倍,即ID5=N·ID4,由上式可以得到:

这里令 得:

得:

因此:

由上可知,得到了一个与电源电压VDD无关的输出基准电流。由于有两条支路电流流过电阻R,第三支路M5、M6流过电流是基准电流的N倍,由(6)式可知:N和R均与IOUT成反比,欲得到一个固定输出的基准电压IOUT,N增加时,可大大减小电阻R的值,从而节省了芯片layout的面积。(本设计N取4)。

1.2带正反馈交叉耦合的差分输入级

在CMOS电路中,电路能够工作的最低电压一方面取决于具体电路的结构形式,另一方面则取决于COMS器件的阈值电压及其过驱动电压[3]。带正反馈交叉耦合的差分输入级电路如图3所示。

在原有的M3、M4 MOS二极管负载上添加了M5、M6两个交叉耦合的正反馈负载。从电路中近似看到最小工作电源电压为1个VTP与3个过驱动电压之和,采用VTH=0.5 V的MOS工艺,最低工作电压可降低1 V左右。为保留一定的余度,本设计电源采用1.2 V。

电路中设置差分对管M1、M2工作在亚阈值区,有利于电源电压的适当降低。通过增加M5、M6,电路输入跨导为:

式中gm1为M1管的本征跨导,由此可以看到输入管的跨导增加了一个因数1/(1-gm6/gm3)。利用这种方法增益改善为:

1.3前馈补偿

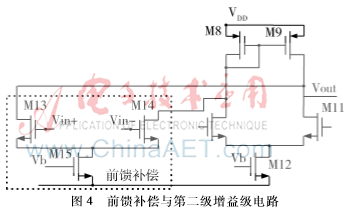

本文在低电压情况下,使用前馈补偿技术取代传统的主次极点分离密勒电容补偿技术。频率补偿是利用前馈路径在高频段中引入左半平面的零点正相移抵消极点导致的负相移[5]。由图4可知,该运放的传递函数具有两个极点和一个左半平面零点,其中ωp1和Z1为:

上式中СO1为第一增益级输出节点总寄生电容,go为输出电导,β为反馈因子。

前馈补偿与第二级增益级电路如图4所示。M8~M11为第二放大增益级;M3/M14为前馈级;M12、M17为各自尾电流管。

第二级及前馈级(A3)放大器的直流增益,各表达式分别为:

通过调节第二级和前馈级的偏置电流与管子宽长比,使得 确保零点位于左半平面。

确保零点位于左半平面。

2仿真结果

基于0.18 μm CMOS 标准工艺实现运放的版图照片如图5所示,在Cadence环境下对运放电路版图后仿真。在工作电压1.2 V,驱动2.5 pF电容负载下,其开环增益和相位曲线如图6所示,该结构能得到增益109 dB,单位增益带宽259 MHz,相位裕度约为73.8°;图7为电路共模抑制比曲线,低频时能达到-80.16 dB。

将本文的性能参数与相关文献对比,如表1所示。从表中可看出本文通过增加少量的静态功耗,在整体性能上均有所改善,能够满足大多数电路的要求。

3结论

本文在传统两级运放的基础上,结合增益自举、前馈补偿等技术,实现了一种新框架的低电压高性能CMOS运算放大器。在满足低功耗条件下,对版图仿真验证,能获得高直流增益和高带宽,系统在稳定性等方面均有较好的性能。该电路能够应用于带隙基准源及各类运算电路中,如加法器、比较器等,具有相当广阔的应用前景。

参考文献

[1] 何乐年,王忆.模拟集成电路设计与仿真[M].北京:科学出版社,2008.

[2] WANG R T,HARJANNI R. Partial positive feedback for gain enhancement of low power CMOS OTAs[J].Analog Integrated Circuits and Signal Processing, 1995(8):21-35.

[3] THANDRI B K,SILVA MARTNEZ J. A robust feedforward compensation scheme for multistage operational transconductance amplifiers with no miller capacitors[J].IEEE Journal of SolidState Circuits, 2003, 38(2):237-243.

[4] CHANG Y S,WU H C,SHIAU M S,et al,Pseudo differential operational transconductance amplifier using common mode feed forward and HD3 feed forward[J].International Symposium on Integrated Circuits, 2011,10(11):250-253.

[5] AKBARI M,BIABANIFARD S,ASADI S.Design and analysis of DC gain and transconductance boosted recycling folded cascode OTA[J].AEU International Journal of Electronics and Communications, 2014, 68(11):1047-1052.