王怡林

(光电控制技术重点实验室,河南 洛阳 471009)

摘要:针对双DSP共享Flash进行程序加载引导的复杂问题,对基于TMS320C6414和ADSP2187的双DSP程序加载引导方法进行了研究与设计。其中TMS320C6414作为主处理器,ADSP2187作为协处理器,共享的Flash芯片连接在TMS320C6414的EMIFB接口上,TMS320C6414通过EMFIA接口与ADSP2187的IDMA接口连接。系统上电后,TMS320C6414首先从Flash芯片读出主处理程序并完成自身加载和引导,然后读出协处理程序,发送给ADSP2187并协助其完成加载和引导。

关键词:TMS320C6414;ADSP2187;共享Flash;加载;引导

中图分类号:TP368文献标识码:ADOI: 10.19358/j.issn.16747720.2016.23.009

引用格式:王怡林. 双DSP共享Flash程序加载引导设计与实现[J].微型机与应用,2016,35(23):31-34.

0引言

在红外目标跟踪领域,随着算法复杂度的提升,运算量增长速度非常惊人,这使传统的单DSP处理系统难以负荷, 因而对复杂的信号处理算法进行分块并在硬件系统上采取多DSP 并行处理的方法势在必行[1]。某信息处理平台是某光电跟踪装置的核心,为满足系统要求,该平台以TMS320C6414和ADSP2187两型DSP芯片为核心进行设计。基于体积、成本等限制,需两个DSP共用一片Flash完成程序存储,并在上电时顺利完成两个DSP程序的加载和引导。本文针对这一要求进行研究,设计了一种两个DSP共享Flash的程序加载引导方法。

1系统方案设计

TMS320C6414是TI公司推出的一款32位定点数字处理器,采用超长指令字结构,一个周期可同时执行8条指令,主频最高达600 MHz[2],内部包括64个用于配置的32位寄存器,还有6个计算单元(ALU),2个乘法器。接口方面具备2个外部存储接口,3个多通道缓冲串行接口, 1个主机接口和通用I/O接口等,还具备EDMA功能。

ADSP2187是ADI公司的ADSP系列的定点数字信号处理器[3],内含3个相互独立的计算单元,即ALU、MAC和桶形移位器。除此之外,还有1个程序控制器(PC),1个可编程的定时器,2个数据地址产生器,以及32 K×24 bit的程序存储空间和32 K×16 bit的数据存储空间。对外接口方面包括1个可编程的Flash I/O,2个串口,1个16 bit的内部DMA接口以及1 B DMA接口(BDMA)。

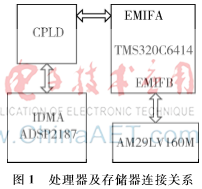

基于两个处理器的特点,本设计将Flash芯片连接在TMS320C6414上,程序的加载和引导由TMS320C6414主导完成。首先对TMS320C6414 的启动模式进行配置。TMS320C6414 的启动模式由其上电时的EMIFB接口地址总线中的BEA[15:14](BOOTMODE[1:0])的连接电平决定, 在复位期间检测这两位的高低电平来决定TMS320C6414的引导模式。本设计将TMS320C6414的引导模式配置成使用默认的8位ROM时序。TMS320C6414完成自身的程序引导后,通过IDMA接口向ADSP2187发送其程序并控制对方完成引导[4]。两个处理器及存储器连接关系如图1所示。

2接口电路设计

要通过TMS320C6414来完成ADSP2187的程序加载和引导,首先要使两者之间建立通信连接,由于两个处理器架构以及对外接口的不同,需要对两个处理器的通信接口进行匹配性设计,以满足数据传输需求。

TMS320C6414的对外通信接口主要有两个EMIF接口、两个McBSP接口、一个HPI接口以及通用I/O等其他接口。ADSP2187主要的对外数据通信接口是IDMA接口,且可通过IDMA完成程序加载和引导。根据这两个处理器接口的特点,基于EMIFA接口和IDMA接口来进行两个处理器的数据通信接口电路设计。

EMIF接口全称为外部存储器接口(External Memory Interface),是C6000系列DSP主要的外部存储器扩展接口,最高数据吞吐率可达1 200 MB/s。可以与目前几乎所有的存储器类型直接连接,包括SBSRAM、SDRAM、SRAM、FIFO等以及其他可以共享内部存储空间的设备。

相比C6000系列其他DSP型号,TMS320C6414的EMIFA接口具有以下特点:

(1)总线宽度达64 bit。

(2)接口时钟可以基于其输入时钟在片内产生,有3种方案:1/6×CPU时钟、1/4×CPU时钟和外部输入时钟。

(3)具有一个可编程同步存储器控制器。

(4)具备PDT信号,可支持外部设备之间的数据传输。

ADSP2187的IDMA接口实质上是一个并行的I/O接口,当ADSP2187作为从机时,主机可通过该接口读/写ADSP2187内部的存储器和寄存器。IDMA接口具有复用的16 bit数据/地址总线,支持对其内部16 bit数据存储器和24 bit程序存储器的访问,对IDMA的访问是完全异步的。

IDMA接口的控制信号包括选择信号(IS#)、读取信号(IRD#)、写入信号(IWR#)和地址锁存信号(IAL#)。当选择信号和地址锁存信号有效时,ADSP2187将总线上的数据当做地址写入IDMA控制寄存器,当选择信号和读取信号有效时,ADSP2187将控制寄存器内地址所指存储单元的内容输出到总线上,此过程构成一个完整的IDMA接口读取操作。写入操作和读取操作的地址传输方式一致,完成地址传输后,将选择信号和写入信号置为有效,待写入数据发送到总线上,ADSP2187将总线上的数据写入IDMA控制寄存器内地址所指存储单元。

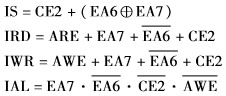

本设计将EMIFA的CE2空间设成16 bit异步接口,数据总线ED15:0与IDMA总线IAD15:0对应连接,EMIFA地址总线EA6和EA7求异或后再与片选信号CE2求或后作为IDMA接口的选择信号(IS#),EA6求非后与EA7、CE2以及EMIFA的读取信号ARW共4个信号一起求与作为IDMA接口的读取信号(IRD#)输入, EA6求非后与EA7、CE2以及EMIFA写入信号AWE共4个信号一起求作为IDMA接口的写入信号(IWR#)输入, EA7和EA6求非、ARE非、AEW非、CE2非共5个信号求与后作为地址锁存信号(IAL#)输入。CPLD具有编程灵活等优点[5],本设计中采用CPLD完成译码。ADSP2187的IDMA接口输入信号运算关系如下:

在TMS320C6414看来,ADSP2187控制寄存器的映射地址是0xA000 00A0,数据寄存器的映射地址是0xA000 0050。

值得说明的是,仅仅完成相关信号的译码和地址映射还不够,还需要对EMIFA和IDMA进行时序匹配。对于IDMA来说,有短周期和长周期两种读/写方式选择,后者需要主机检测IACK信号的状态来判断IDMA是否准备好。本设计选用短周期读/写操作,其写入操作的时序图如图2所示。

本设计中,EMIFA时钟设置为1/6×CPU时钟,CPU时钟为480 MHz,则EMIFA时钟为120 MHz。EMIFA接口CE2空间的时序由寄存器CE2CTL控制,主要包括建立时间、处罚时间、保持时间三项参数设置,三项参数均以时钟周期数来表示。

根据图2中IDMA接口的时序要求,建立时间、触发时间和保持时间的总和应大于tIWP,换算后3项参数的和应大于等于2,同时保持时间应大于tIDH,将CE2CTL相应参数设为1即可。

TMS320C6414向ADSP2187写入数据的流程为:先向地址0xA000 00A0写存储地址,然后向0xA000 0050写入待写数据即可完成写操作。读操作的时序匹配方法和流程与写操作相似,不再详述。

3TMS320C6414加载引导方法

当光电跟踪装置上电后,TMS320C6414 进入复位状态,完成复位后, 其只能先将1 KB大小的程序代码自动加载到内部RAM。通常情况下,光电跟踪装置的信息处理程序规模远远大于1 KB,为了完成整个程序的加载和引导,必须编写一段程序搬移代码来将整个信息处理程序搬运到内部RAM,并且搬移低代码的大小不能超过1 KB,按照TMS320C6414用户手册的要求,须用汇编语言完成,搬移程序在完成了信息处理程序的搬运后,须将PC指针指向信息处理程序的入口,自此信息处理程序才能开始运行,进而完成目标识别和跟踪任务。完整的搬移程序的代码及注释如下:

…………;

//相关寄存器初始化工作结束

S_R .setb4

D_R .seta4

//将程序长度、RAM首地址、Flash首地址的存储首地址拷贝进寄存器A3

mvklcopy_table, A3

mvkhcopy_table, A3

//程序加载开始

copy_section_top:

ldw *A3++, B0//将程序长度加载到B0

ldw *A3++, A4//将运行首地址加载A4

ldw *A3++, B4//将程序在Flash中的首地址加载到B4

nop 2

[!b0]bcopy_done//判断拷贝是否完成

nop5

shr B0,2,B1//将B0除以4后加载到B1

//开始进行程序加载

copy_loop:

ldw*S_R++,B5

|| mvB1, A1//待拷贝长度加载进A1

|| subB1, 1, B1//长度减1

//将程序从Flash读入B5

[B1]ldw*S_R++,B5

||[B1]subB1, 1, B1

//将B5中的程序加载到RAM中

stw B5,*D_R++

||sub A1, 1, A1

[A1]stwB5,*D_R++

||[A1]subA1, 1, A1

[B1]bcopy_loop//判断是否完成加载

nop5

//跳转到开始处进行下一段的加载

bcopy_section_top

nop5

//加载完成,对相应的寄存器进行设置

copy_done:

mvkl0x01840000,A4

mvkl0x0300,B4

mvkh0x01840000,A4

mvkh0x0300,B4

stw B4,*A4

nop 5

mvkl .S2 _c_int00, B0

mvkh .S2 _c_int00, B0

B.S2 B0

nop 5

//各段长度、RAM首地址、Flash首地址设置

copy_table:

; .text//代码段长度

.word 0x00029220

.word 0x00000400

.word 0x64010400

; .cinit//变量段

.word 0x00002dcc

.word 0x000460e0

.word 0x64039620

.word 0x0//所有段结束标志

4ADSP2187加载引导方法

ADSP2187支持从片外ROM和IDMA接口引导两种方式,非常方便用户设计系统的需要[6]。本文所述信息处理机采用从IDMA接口引导的方式实现预处理程序的加载引导,ADSP2187上电后,从IDMA接口接收主处理器TMS320C6414传输的程序并执行。

ADSP2187函数根据在存储器中所处的位置分为函数段、数据段,函数段和数据段又根据所处的OVERLAY页面再分为不同的段[7]。每段前3个数据标示了该段的数据长度、该段在存储区域的首地址和该段所处的页面。该段数据处于函数区还是数据区由首地址的14位标示。

TMS320C6414首先对ADSP2187进行复位操作,然后从Flash中读取该段数据的函数区字节数、函数区首地址和函数段所处的页面,再从Flash中搬移1 B,通过IDMA口写到ADSP2187的函数区,写完后再从该函数区地址读出数据并与所写的数据进行比较,如果不相等则重新写该地址和校对,循环TryCycle次退出;如果相等,则进行下一个字节的传输,直到该段数据全部传输到ADSP2187中。同样地,TMS320C6414再把其余数据通过IDMA口传输到ADSP2187中,最后在ADSP2187的0地址写数启动ADSP2187运行,并以此判断整个循环的结束。因为ADSP2187函数区数据为24 bit,因此对函数区数据读写时需要同时读取2 B数据。

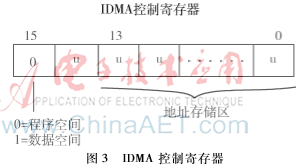

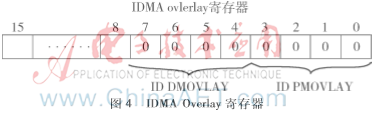

对ADSP2187芯片IDMA接口的读写,通过对IDMA的控制寄存器和OVERLAY寄存器的操作来实现。寄存器各位定义如图3、图4所示。

对ADSP2187IDMA口的操作需要先对IDMA口控制寄存器和OVERLAY寄存器进行配置,说明需要读取的数据是程序区还是数据区、在哪个页面中、地址为多少,然后对总线进行读写操作,从而实现对ADSP2187内部存储区的读写。

得益于接口电路的作用,TMS320C6414可以通过对地址0x03200000的操作来实现对IDMA控制寄存器和OVERLAY寄存器的配置,当写到该地址的数据最高位为1时,对OVERLAY寄存器进行操作,为0时则对控制寄存器进行操作;可以通过对地址0x03100000的读写实现对数据总线的读写。ADSP2187的程序加载引导逻辑流程如图5所示。

5结论

本设计实现了TMS320C6414和ADSP2187两个DSP芯片共享Flash的程序引导加载,该设计已成功应用于某光电跟踪装置上,较好地完成了信息处理程序的加载和引导,工作稳定可靠。本文设计方法为将来其他多DSP共享Flash的信息处理机设计提供了参考,有着重要的实际意义。

参考文献

[1] 李宏,李伟,李蒙,等.基于多DSP的红外目标跟踪系统设计与实现[J]. 电子技术应用,2006,32(8):59-61.

[2] 杨明,赵晓博,狄卫国,等.基于TMS320C6414的大容量存储器扩展设计[J]. 自动化技术与应用,2008(6):103-105.

[3] 王冬,李登科.基于双DSP的信息处理机设计[J].国外电子测量技术,2013,32(6):89-92.

[4] 赵熠,景德胜.一种基于双处理器的信息处理平台的设计[J].电子技术设计与应用,2015(6):86-87.

[5] 陈诚,陈晓平,王识君.基于DSP+CPLD的电动舵机控制系统的设计[J]. 电子技术应用,2015,41(4):84-86.

[6] 陈勇,贾明永,董德新,等.ADSP2187L在某光电跟踪装置中的应用[J].航空兵器,2004(4):22-24.

[7] 梁楷.ADSP218X的IDMA接口设计[J].网络财富,2010(21):183.