李炳乾,王勇,刘达,谭小虎

(空军工程大学 航空航天工程学院,陕西 西安 710038)

摘要:航电光纤通道接口板是实现航电系统统一网络的基础,在高速传输过程中,光纤通道接口板需要及时对未处理的帧进行缓存。文章基于DDR2的大容量、高速率存储模块为这一问题提出了解决方案。对DDR2的功能及结构进行了简要阐述,根据输入和输出需求,设计实现了DDR2芯片组电路,采用FPGA IP核实现DDR2控制器,测试仿真控制器的读写时序。测试结果表明,所设计的DDR2控制器能够按照规则的时序进行操作,实现了高速读写,可以实现功能集成并节约成本,很好地满足光纤通道接口板的设计需求。

关键词:光纤通道;DDR2控制器;FPGA;IP核

中图分类号:TP27文献标识码:ADOI: 10.19358/j.issn.16747720.2016.23.010

引用格式:李炳乾,王勇,刘达,等. 航电FC接口板存储模块设计与硬件电路实现[J].微型机与应用,2016,35(23):35-37,41.

0引言

光纤通道(Fibre Channel,FC)总线接口板是综合模块化航电系统结构中的重要组成部分,依据航电系统网络中心化设计要求,光纤通道总线接口板要实现数据的接收与发送[1]。由于数据传输量巨大,为减轻主机CPU收发处理负担,还要具备包括数据缓存在内的多种功能。数据缓存功能就是要构建光纤通道接口板数据的接收和发送队列,缓存未及时处理的数据和接口板状态信息。

DDR2作为当前主流的内存芯片,具有存取速度快、储量大、成本较低等特点[2-3],被广泛地运用到通用计算机系统、嵌入式系统等电子行业的各大领域当中。根据课题要求,采用DDR2可以满足需求,因此,充分利用板上已有硬件资源,包括FPGA、DDR2芯片等,在FPGA中进行DDR2控制器设计,实现航电光纤通道接口卡上的存储模块设计。

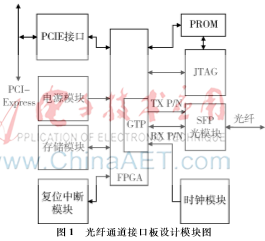

光纤通道接口板的整体功能模块设计如图1所示。

光纤通道接口板传输速率为1~2 Gb/s,缓存数据读写量大,必须采用高速电路设计,因此时序的严格约束十分必要,存储模块的合理设计占据光纤通道板卡设计十分关键的地位。

1DDR2性能与结构特点

1.1DDR2性能特点

DDR2(全称为Double Data Rate 2) 是一种可以在时钟上升沿和下降沿进行数据传输的内存技术标准,由电子设备工程联合委员会(JEDEC)负责标准的开发和制定[1]。由于DDR2芯片采用4n-bit 预抽取架构以实现高速操作[4],每个IO引脚被设计为每个时钟周期可传输2个数据字,在不改变内核时钟频率的情况下实现了数据传输速率的加倍增长。

1.2DDR2结构特点

光纤通道接口板设计选用的是2G容量的DDR2芯片MT47H128M16RT[4],其芯片内部包括控制逻辑、地址注册、BANK控制逻辑、存储阵列、IO接口和时钟等,存储阵列设有8个内部Bank,每个Bank大小为16 384×256×64=256 MB,以实现并行读写操作。

在芯片外部,双向数据选通引脚DQS和DQS#用于接收端及时获取数据,当处于READ工作状态时信号由DDR2发送出去,反之由存储器控制器发送,本设计选取的芯片数据宽度为16 bit,分为高8位和低8位。此双向数据选通分别由LDQS、LDQS#和UDQS、UDQS#信号进行控制。与此同时,DDR2 SDRAM工作于差分时钟下,当CK上升、CK#下降时,表示时钟的正边沿。控制命令(地址A[13:0]/BA[2:0]和控制信号CS#等)在时钟的正边沿触发,数据在DQS(同时也是时钟CK)的双边沿触发。

2光纤通道接口板存储模块硬件设计

2.1存储模块供电设计

光纤通道接口板采用美光(Micro)公司生产的MT47H128M16RT-25E:C型号84脚FBGA封装DDR2 SDRAM芯片。DDR2工作电压采用的SSTL_1.8标准较DDR的SSTL_2.5有较大的优势,能够很好地减小板上功率消耗和热量生成。设计中,将FPGA生成的1.8 V电源引脚接入DDR2电源引脚VDD、VDDQ、VDDL等,为DDR2芯片供电。

与此同时,DDR2芯片还需要直流0.9 V的参考电压VREF输入,参考了Xilinx公司ML555 developing kit中的电源电路设计,利用PTH05050Y芯片对DDR2的0.9 V供电电源进行稳压。由于DDR电路VREF消耗电流很小,因此将1.8 V直流电源电压经串联电阻分压处理,得到0.9 V作为芯片输入参考电压VREF,PTH05050Y输出电压为0.9 V经过稳压的DDR2参考电压。

2.2接收/发送缓存芯片组设计

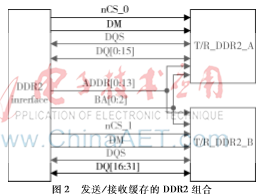

DDR2 SDRAM负责存储从FC-1层发往FC-0层的待发送帧和从FC-0层发往协议层的接收帧,由于光纤传输速率快,需要大容量的缓存单元,同时,接收与发送端口同时对存储器中某一地址进行操作可能引起未知错误,产生不可预测的后果。因此,利用4片MT47H128M16RT DDR2芯片两两组合分别设置为发送缓存和接收缓存,如图2所示为两片DDR2芯片组成的接收/发送数据缓存模块。

两片DDR2构成的数据缓存需要32条数据线,而选用的MT47H128M16RT芯片只有16条数据引脚,因此将32位数据线分为高位和低位,分别接入两片DDR2存储芯片,存储器控制器通过控制片选CS#、命令输入RAS#、CAS#和WE#等引脚,实现数据的读写操作。

利用DDR2所具有的OCD、ODT和POST CAS功能可以很好地对输出信号品质进行控制和调整,使内存单元模块的设计更为简化和精确。通过离线驱动调整(OCD)功能设置上拉/下拉电阻,实现对DQS和DQS#、DQ和DQ#的电压调整,使DQ与DQS的电压相同,减小DQ-DQS倾斜,提高信号完整性和信号品质。参考上一节DDR2芯片内部结构,DDR2芯片数据DQ、数据选择DQS端引脚设有内建核心终结电阻(ODT),因此在设计中,将ODT引脚经下拉电阻接地,芯片初始化时接低电平,在读写数据时置高启动ODT功能,减少主板上电阻的设置数量,同时也提高了信号质量。

3DDR2控制器设计

3.1DDR2控制器功能

DDR2 SDRAM是光纤通道接口板的核心组件,硬件的搭建基于DDR2的接口板,更重要的是通过严整的时序和规范的操作控制对DDR2进行初始化、数据读写等,DDR2控制器就是完成这样工作的部件[5]。根据实际使用需要,本文设计的DDR2控制器主要实现的功能如下:

(1)完成DDR2的初始化操作;

(2)可对DDR2参数进行配置;

(3)完成突发长度为4的读写操作;

(4)自动发送激活和预充电控制命令,减少用户对底层控制时序的复杂定义;

(5)自动刷新操作。

3.2基于FPGA的DDR2控制器设计

DDR2控制器设计包含4个主要模块:时钟生成模块、存储控制模块、数据链路模块和用户接口模块,如图3所示。

时钟生成模块为控制器提供时钟信号,输出多相位时钟,同时对DQ与DQS间的时延进行校准,使DQS边沿准确对齐DQ有效窗口的中心位置。

读写接口模块负责将用户数据DQ和数据选择DQS信号按照规定时序写入DDR2;从DDR2读取数据时,DDR2发送DQ和DQS信号,FPGA将DQS信号经延时校准后作为其写时钟,读取DDR2数据。

存储控制模块为数据读写提供地址和命令信号。组成在DDR2上电复位后进入初始化进程。DDR2经过20 μs的稳定期,CKE时钟使能信号置高,400 ns后开始预充电操作,配置寄存器后再次预充电和刷新,判断时钟是否锁定后配置离线驱动电压,完成初始化。在初始化完成后,可进行数据读写。刷新操作优先级高于读写操作,因此两者冲突时控制器将通知用户停止发送读写命令,待刷新操作完成后进行读写操作。

DDR2读写操作采用的是突发(burst)模式,需要读写命令、读写数据和读写地址,在读写突发操作完成时发送突发信号完成(burst_done),保持两个时钟周期有效后终止读写操作。

光纤通道板卡采用Xilinx公司生产的Virtex-5系列XC5VLX85T进行逻辑设计,在设计光纤通道协议逻辑后,FPGA的空置逻辑可以进行DDR2控制器的逻辑设计,在充分利用FPGA上资源的同时节约了板上另外焊接专用DDR2控制器芯片的成本和空间。

在Xilinx ISE开发套件中提供有存储器接口生成器(Memory Interface Generator,MIG)IP核开发工具,可以直接根据用户需求例化与硬件设备相适应的DDR2存储控制器设计模块[6]。MIG具有GUI界面,根据需要可以对存储器件的类型、位宽、速度级别、控制参数和引脚分配进行准确配置,大大缩短设计DDR2控制器的时间周期,尤其对系统设计很有帮助。

在设计过程中无需再了解DDR2严格的物理层时序及工作特性就可以设计实现DDR2的读写功能,用户操作流程如图4所示,满足设计需求。

上电后,通过初始化配置,得到置高的init_over信号,说明初始化成功;将标识START信号置1,并通过WRITE_BUSY[1]和READ_BUSY[1]信号判断是否满足命令发送条件,当两位均为1时允许命令发送。若发送命令条件满足,则通过用户接口发送CMD、操作首地址CMD_ADDR和数据操作计数CMD_CNT,若WRITE_BUSY[0]和READ_BUSY[0]互斥取0值时,用户接口完成响应的写入或读取数据的操作。

4调试过程与结果分析

4.1测试过程

设计采用内部状态机实现对FPGA DDR2 IP核控制信号、读写数据信号、地址信号输出和输入的数据采集。测试机理为:利用FPGA上DDR2控制器对外部硬件DDR2执行一个burst写操作,然后在同一地址执行相同burst的读操作,读取刚写入的数据,对比写入数据与读出数据是否一致。

DDR2硬件验证测试流程如下:

(1)系统复位;

(2)等待用户接口信号“init_over”为高;

(3)对DDR2进行写操作;

(4)对DDR2进行读操作;

(5)对比读出数据与写入数据是否相同,若相同ERROR置0,反之置1。

4.2调试结果

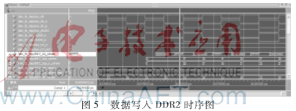

测试程序向DDR2中发送一个Burst=4的数据,写入数据的时序如图5所示。

然后对数据进行读取,读取数据的时序如图6所示。

在init_over得到高电平后,初始化完成,在相同地址进行数据的写入和读取,从中可以看到写入DDR2和读取到FPGA中的数据一致,说明数据操作正确。

5结束语

基于FPGA设计的DDR2控制器可以很好地满足时序关系,经过对输入输出数据的比较表明,数据一致,读写速度达到了光纤通道接口板的设计需求。

参考文献

[1] 支超有,唐长红.机载数据总线技术及其应用[M].北京:国防工业出版社,2009.

[2] 陈平,张春,张一山,等.DDR2 SDRAM 控制器IP功能测试与FPGA验证[J].微电子学,2016,46(2):251-254.

[3] JEDEC solid state technology association. JEDEC Standard: DDR2 SDRAM Specification[EB/OL].(2006-07-01)[2016-07-10], http://www.jedec.org/download/search/JESD792C .pdf.

[4] Micron. DDR2 SDRAM MT47H128M16XX Datasheet,2010[EB/OL].[2016-07-01].http://download.micron.com/pdf/datasheet/dram/2g_ddr2.pdf.

[5] Xilinx Inc. Ug086.pdf. 2011[EB/OL].(2006-07-01)[2016-07-10].http://www.xilinx.com/support/documentation/ip_documentation.

[6] 范泽明.DDR2 SDRAM 控制器设计与验证[D].西安:西安电子科技大学,2009.