IMEC:光刻的另一种方法

2020-09-03

来源:半导体行业观察

光刻技术是使微电子和纳米电子器件在过去半个世纪中不断微缩的基础技术之一。该过程使用光将图案从光掩模转移到基板上,然后进行一系列化学处理,将曝光的图案蚀刻到基板上,或以所需的图案沉积新材料。

随着进一步的微缩,这种传统的自上而下的图案转印过程变得越来越复杂和昂贵。器件的进一步小型化要求对关键尺寸低于20nm的特征进行patterning。除了缩放分辨率外,精确的图案放置也变得非常具有挑战性。随着高纵横比和复杂形状的3D结构的出现,有效占用空间的减少也随之而来。

大约五年前,该行业开始对诸如区域选择性沉积(area-selective deposition:ASD)和定向自组装(directed self-assembly:DSA)之类的其他图案化方法感兴趣。这些自下而上的技术有其自身的优点和挑战,但是它们有一个共同点:它们可以提供新颖的解决方案,因此具有巨大的潜力来补充传统图案,以用于未来纳米电子器件的工业制造。

DSA:缩小密集的规则图案

从历史上看,通过在光刻系统中应用较短波长的光源,可以对越来越小的和更密集的特征进行图案化。过去这些年,波长已从436nm,405nm,365nm,248nm和193nm减小到最终的13.5nm,也就是我们熟知的极紫外(EUV)光刻。对于给定的波长,已经引入了多种图案技术的变化,以进一步推动分辨率极限。如今,工业界正在使用例如光刻,平版印刷工艺(涉及两个曝光步骤)或自对准双(甚至四)图案化。后一种技术依赖于一个光刻步骤(以创建预图案)以及附加的沉积和蚀刻步骤(以实现原始预图案的复制)。已知这些多图案化过程非常复杂且昂贵。

几年前,DSA已被提出作为一种有前途的互补图案选择。DSA基于称为BCP(block-copolymers )一类分子的自组装特性。在适当的情况下,这些材料在涂覆到晶圆上时会发生微相分离(microphase separatio)。这就可以获取具有5-30nm特征的规则纳米尺寸图案。可以通过调节聚合物的组成及其尺寸来设计图案。通过使用线/间隔或孔的预图案,可以进一步指导(指导)该装配体,这是半导体行业感兴趣的两种结构。这样,最终图案化的pitch将比template的小得多。由此可见,DSA是一种非常规的自底向上技术,可以增强图案的密度和分辨率。

主要优点和挑战:

IMEC已经确定了其多项优点,以评估DSA流程与大批量生产的相关性。Imec认为与传统的多图案技术相比,成本(COO)是DSA的主要优势。较低的COO可以主要归因于减少的工艺步骤,并结合使用传统的光刻技术来创建更宽松的预图案。英特尔在2019年IEDM会议上提出的第二个优势是轻松控制边缘放置错误的能力,这是传统图案化方法遇到的主要挑战之一。使用DSA,可以以非常均匀的方式在整个图案化区域上获得紧密的pitch。

但是,DSA虽然比传统的(EUV)光刻简单,但DSA的设计灵活性却较低。DSA可以轻松打印常规图案,但是很难打印非常规图案(例如,pitch可变的图案)。因此,将来的设计在采用DSA作为构图技术时将不得不接受这一限制。“了解DSA设计”将是今后几年要解决的重要挑战。

缺陷率:不再是最卖座的产品:

最初,半导体行业对DSA并不那么乐观,因为控制缺陷率变得非常困难。为了与工业制造相关,总缺陷密度应在1cm -2以下,这在当时很难实现。在自组装过程中形成的位错和桥接是造成总缺陷的主要原因。

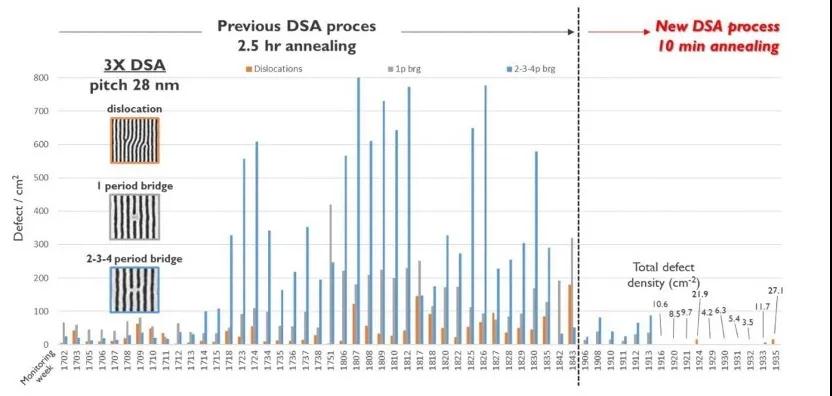

但是,今天,imec很有信心充分控制缺陷率。近年来,imec深入研究了annihilation ,并获得了有关如何控制位错和桥接的基本见识。最终,该团队能够将退火时间从最初的2.5小时减少到只有10分钟,从而获得具有稳定且足够低的缺陷数的有序状态。如果我们使用传统的电子显微镜,则需要一年多的时间才能发现缺陷。有了这些见解,imec现在可以为行业提供一本手册,其中包含一些主要 knobs ,借助这些 knobs 可以控制DSA流程的缺陷(图1)。

图1. 2017年至2019年的DSA缺陷监视结果。

通过提高吞吐量可以实现更低,更稳定的缺陷率。

迈向第二代BCP:

这种稳定且低缺陷的DSA工艺是通过使用3倍图案密度乘法实现的。可以使用BCP的DSA在84nm间距的预图案上成功地图案化28nm的最终图案间距,该预图案是通过193nm浸没光刻技术获得的。通过使用PS-b-PMMA (polystyrene-block-poly methyl methacrylate) 作为BCP,可以实现3x图案致密化。

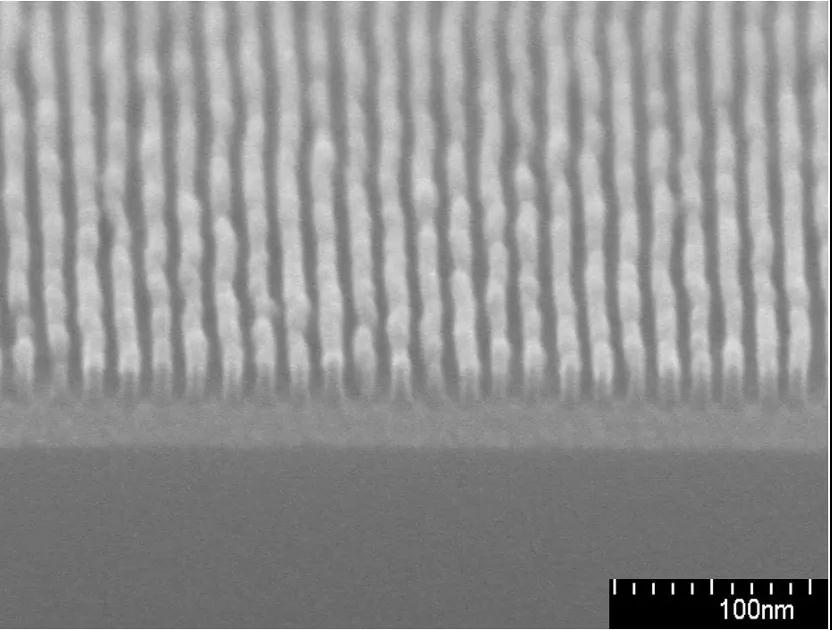

随着imec朝20nm以下的间距发展,BCP链的长度也应减少,以实现更小的间距。然而,小于间距21nm的PS- b - PMMA聚合物将不再形成透明结构,从而使BCP处于混合无序状态。为了解决这个问题,imec现在正在与材料供应商和大学密切合作,转向第二代BCP,即高X BCP。迄今为止,使用PS- b -PMMA获得的知识已转移到新一代BCP中,从而导致了良好的自组装过程(图2)。

图2.高χDSA生成的16nm全pitch L / S模式。

(图片来源:Jan Doise /明尼苏达大学/德克萨斯大学奥斯汀分校)。

目前,尚在调查一些剩余的问题。首先,在这种微小的情况下,将图案转移到底层材料中比想象中更具挑战性。其次,需要开发新的计量技术,以能够评估现在尺寸非常小的自组装结构的缺陷性。

大约10年前,imec开始探索使用DSA作为替代图案方法的想法。当时,DSA主要是一个学术研究领域。基于近年来取得的进展,DSA现在在工业领域引起 了巨大兴趣。这种发展伴随着大学,材料和设备供应商以及计量学家的巨大承诺,即认真控制和检查材料和过程。这个生态系统是成功的关键,对于下一代DSA流程的开发也是如此。

ASD:仅在需要时存放材料

对于区域选择性沉积,将根据预定义的图案沉积材料,而不会在其余表面上发生沉积。该选择性沉积可以通过依赖于选择性表面反应的沉积技术来实现,例如原子层沉积(ALD)和化学气相沉积(CVD)。

几年前,这种自下而上的技术也引起了半导体行业的兴趣,因为它是对传统的自上而下的pattering进行补充的方法。就像DSA一样,ASD也有自己的优点。与传统光刻相比,它可以实现更广泛的应用,例如在复杂的3D结构中构图特征。ASD的另一个巨大机会是,它原则上只能在需要的地方放置结构,并且在水平和垂直方向上都具有原子精度。这样,对于某些应用,它可能会成为一种更具可持续性和成本效益的方法,与自上而下的图案相比,所需的化学产品和能源更少。

到目前为止,ASD的工业用途仅限于半导体的选择性外延生长和互连结构中纳米级金属薄层的生长,这主要是因为仅对有限数量的工艺和材料进行了研究。为了扩大该技术的适用性,必须对表面化学,ALD和CVD工艺的表面依赖性以及前体在这些工艺中的作用有基本的了解。

另外,必须具有控制或减轻非生长区域缺陷的能力。自2016年以来,每年在ASD研讨会上都会讨论该领域的全球进展。在本次研讨会上越来越多的科学贡献反映出学术界和工业界对这一引人入胜的研究领域的兴趣日益浓厚。

对表面化学和改性的深入了解:Imec成功地探索了几种材料系统,这些系统有望选择性沉积诸如TiN或Ru之类的材料,这些材料与芯片制造高度相关。据证实,例如,OH–等的SiO2 终止电介质可以用作用于生长的Ru的生长表面起作用。

图3. 7.5nm厚的TiN,用ALD选择性沉积在Si3N4(空间)上。

aC(线)充当非增长区域。

广泛的潜在应用:

对ASD期间的表面化学和生长机理的更深入了解将指导新颖的ASD工艺的设计,从而实现更广泛的应用。潜在的应用包括例如创建完全自对准的通孔。通孔是金属结构,可将芯片后端的不同金属层电互连。传统上,通孔的形成始于对通孔开口进行图案化并将其蚀刻到下层中。然后在通孔中填充金属(例如钌(Ru))并进行过度填充,这意味着金属沉积持续到在底层上形成完整的金属层为止。蚀刻步骤和化学机械抛光步骤完成了通孔的形成(图4)。通过这种方式,如果通孔过大或未对准,则存在短路或可靠性问题的风险。相反,利用电介质上的电介质ASD,由于创建了形貌,因此可以放宽通孔的对准和过大规格。

图4. 8nm厚的电介质,通过ALD有选择地沉积在低k上。

被甲基封端的有机膜功能化的铜线充当非生长区域。

其他潜在的应用是色调反转(tone inversion)过程,通常可以获得逆的材料图案。这样,它们可用于将孔变成柱子,或将空间变成线。ASD是用于此类应用程序的有前途的技术。使用预构图的牺牲层作为模板,通过使用区域选择性沉积,通过自下而上的填充获得反面的材料图案。当难以对材料进行传统的光刻构图时,例如对于TiN或Ru之类的硬掩模材料,使用ASD进行色调反转可以提供解决方案。此外,由于不需要过量填充和CMP步骤,因此该解决方案比传统方法需要更少的处理步骤。用于音调反转的ASD也可以扩展到较小的特征尺寸。

对于极端狭窄的沟槽或孔(例如,互连过孔),甚至高纵横比的结构(例如,Supervia),或垂直放置在复杂的3D结构(例如,垂直孔)中,ASD也是一种候选方法。互补场效应晶体管(或CFET)。潜在的应用不限于此处列出的那些。

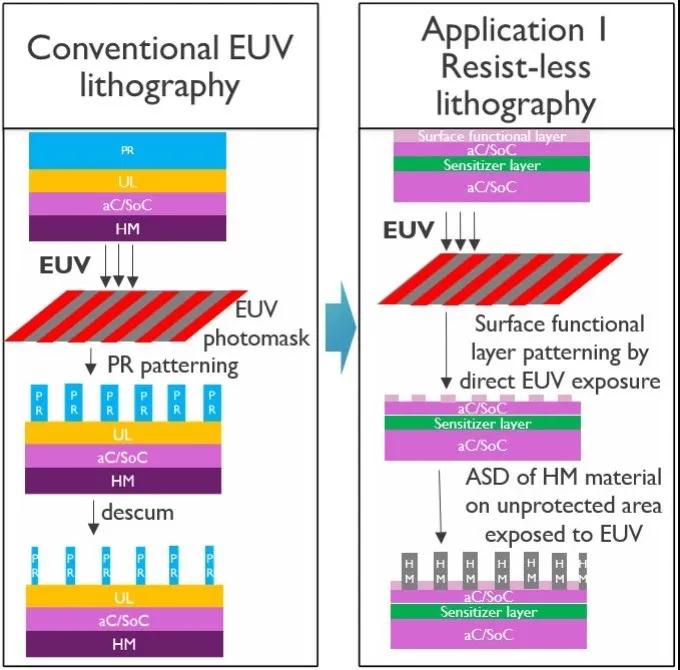

一种破坏性方法,无抗蚀剂光刻:

更具有破坏性的是,imec正在探索ASD作为替代无抗蚀剂光刻方法的潜力,以支持高NA(0.55数值孔径(NA))EUV光刻工艺。高NA光刻有望成为下一代EUV光刻工艺,有望推动半导体规模向3nm以下技术节点发展。具有高数值孔径光学器件的EUV光刻通常需要非常薄的光刻胶层,很难均匀地实现。而且,当前的光致抗蚀剂材料具有非常复杂的化学组成。当暴露在EUV光下时,暴露区域和未暴露区域之间的侧壁可能会显示出较高的粗糙度,从而导致有效特征尺寸发生波动。

在寻找用于高NA EUV光刻的最佳光刻胶材料的同时,imec正在研究在不使用光刻胶材料的情况下创建光刻图案化掩模的可行性(图5)。

图5.无抗蚀剂的EUV光刻(右)与常规EUV光刻(左)的概念。

就像传统的EUV光刻一样,无抗蚀剂光刻也使用EUV光子发射。但是在这种情况下,仅顶表面需要暴露在光源下,从而可以减少暴露所需的EUV剂量。

如今,支持ASD的EUV光刻的主要目标是与相关材料的区域选择性沉积相结合,以建立对表面改性机制的基本理解。此外,这项工作的基本部分是研究EUV光与改性和未改性材料表面的相互作用。这项研究在很大程度上受到建模工作以及Attolab中即将可用的工具的支持。Attolab是imec和KMLabs的一项联合计划,最近成立的目的是使研究EUV光子吸收及其后续过程的时间跨度达到前所未有的范围。

总结

DSA和ASD都被认为是有前途的自下而上的构图方法,可以补充传统的自上而下的构图方案。当图案化密集的规则结构时,DSA是一项冠军技术。与传统的图案化相比,该技术有望降低拥有成本,并降低边缘放置误差。Imec控制缺陷的能力是迈向工业应用的重要一步。另一方面,ASD是一种新颖的方法,它允许以很高的精度仅在需要的地方放置结构。只要能够充分理解表面化学,表面钝化和沉积机理,并控制缺陷率,该技术就有望在芯片制造领域得到广泛的应用-从色调反转到无抗蚀剂光刻。