谈台积电与三星5nm异同,是谁翻车?

2021-01-28

作者: 黄烨锋

来源: 电子工程专辑

“5nm翻车”也算是近期的一个热门话题了,似乎去年下半年发布的,包括骁龙888、麒麟9000、苹果A14等在内的一众应用了5nm工艺的手机芯片,都在功耗和发热表现上不够理想。

骁龙888(小米11)跑个Geekbench 5,单CPU功耗就达到了7.8W,堪称骁龙近代能耗比最差,Adreno GPU性能首次逊于隔壁Mali;而麒麟9000(华为Mate40 Pro)虽说GPU性能上去了,但在光明山脉测试中,跑出了11W的峰值功耗;这都是向着PC功耗看齐的节奏了。很多媒体也因此将5nm冠以“集体翻车”的名号。

高通骁龙888、三星Exynos 2100选择三星5nm,而海思麒麟9000、苹果A14选择了台积电5nm。事实上,即便都叫5nm,台积电和三星的5nm工艺也差异甚远——所以“集体翻车”这种说法首先就值得商榷。这两者甚至不该直接比较。本文我们根据Wikichip、Semiwiki、Semiconductor Digest等机构所做的研究,尝试谈谈两家5nm工艺的一些基本差异。

虽说从微观层面,比如材料、晶体管性能等无法直接比较;而且台积电甚至没有公开5nm工艺晶体管的关键尺寸(暂时也没有5nm工艺的相关“拆解”)。本文仅尝试给出两者大方向上的差异。

虽说主流芯片功耗爆表是否真的与台积电、三星的5nm工艺有关,个人持保留意见。但通过这篇文章,我们也能更好地理解,如今的尖端工艺发展成了什么样。

到底晶体管的哪个部分是5nm?

在探讨两种5nm工艺差异前,首先仍需明确一个概念。即现在的“几nm”工艺这样的称谓,顶多就是个营销概念。不管是7nm还是5nm,晶体管或者芯片微观层面,都不存在哪个几何参数是7nm或5nm。如此一来,5nm也就名副其实地成为了一个虚指,它仅能用于表达一个工艺节点,“5”不存在实际意义。

早在1997年以前,几点几微米或几百纳米工艺,的确是指晶体管上gate(栅或闸)的长度(Lg)。比如0.35μm,350nm,确实就是指gate长度为350nm。在350nm制造工艺以前的时代,工艺数字步进以0.7倍为节奏,比如350nm x0.7,下一代工艺就该是250nm了。

FinFET结构晶体管

不过到了奔腾3时期的250nm工艺,实则已经不再真正指代晶体管gate长度。250nm节点的gate长度已经来到了190nm,但晶体管的其他部分却无法以对等的比例来同步缩减。从这一时期开始,工艺节点的这一数字便不再具有太大的实际意义。2012年22nm节点问世时,随之而来的FinFET晶体管结构。这种3D结构要用一个数字来衡量晶体管尺寸也更难了。

在20nm以后,越来越多的节点数字也抛弃了0.7倍步进的传统。14nm、7nm、5nm虽然仍遵循0.7倍步进传统,但12nm、8nm、6nm、4nm等则显然更具营销意味了。自不必说,这些数字本身,除了表达工艺迭代之外,便再无更多意义。

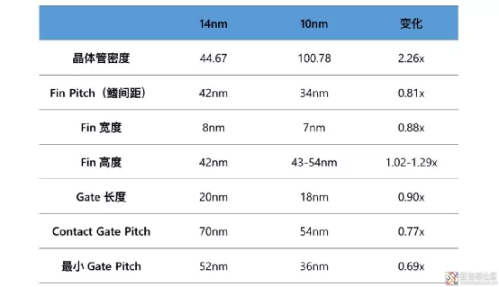

若一定要说在晶体管上,与如今这个节点数字还有所关联的部分,那大概就是fin宽度了,上面这张图是Intel的14nm与10nm两代工艺,晶体管各关键参数的变化,其中fin宽度大致与节点数字是一个量级。

台积电5nm与三星5nm的本质差异

我在去年《同样是台积电7nm,苹果和华为的7nm其实不一样》一文中曾大致总结过,台积电与三星7nm可认为是同代工艺,从Wikichip预估的数字来看,这两者的晶体管密度(高密度库)应该也差不了多少。

但这两家fab的工艺路线方向却已经发生了较大差异。在7nm时代,三星foundry以更激进的姿态,率先在多个叠层采用了EUV(极紫外)光刻。台积电的7nm路线图中,至少N7与N7P工艺仍然没有采用EUV,直到N7+才用上了4层EUV光刻层。

台积电N7+工艺的情况比较特别。市面上选择了N7+的芯片似乎很少——知名的大概也就是Kirin 990 5G版了(Kirin 990 4G版用的是N7工艺)。而且N7+与N7/N7P并不兼容。

台积电N7后续的完整迭代自然就是N5了——节点数字也符合0.7倍步进的节奏。所以对台积电而言,5nm的确就是7nm的迭代工艺。

但三星这边可不一样。三星近些年的路线演进,开始走完整迭代时的大步子。比如在三星眼中,10nm到7nm属于节点的完整迭代,所以7LPP就相对激进地用上了EUV。在7LPP往后,三星foundry路线图的完整迭代,下一代工艺应该是3nm(3GAA)。且7nm->3nm的工艺迭代,迈的大步在于晶体管结构从FinFET,演进至GAAFET(Gate-All-Around FET)或/和MBCFET,也就是传说中的纳米线和纳米片。

而5nm在三星眼中实则属于1/4代工艺,或者说5LPE属于7LPP工艺的同代加强,是向3nm工艺的过渡。三星的7nm与5nm的关系,更类似于其10nm与8nm的关系,如上图所示。三星7LPP工艺同代加强,还包括了6nm、5nm、4nm。

如此一来,台积电和三星(以及Intel)未来的工艺迭代可能要进一步发生分歧。比如台积电预期中的3nm,至少前期并不打算采用GAA结构。当然,3nm就属于题外话了,而且虽然三星的3GAA工艺PDK前年就进入了Alpha阶段,但其量产至少也要等到明年。

这种迭代节奏上的差异(以及双方7nm的起点差不多),导致了台积电在5nm节点上跨的步子,会明显比三星更大,或者说更先进。至于后续3nm如何,尚不得而知。所以N5与5LPE理论上是两家公司的两个不同产品,而不应将其理解为某个固定标准下,双方各自交出的答卷。

两种5nm工艺的晶体管密度

鉴于篇幅关系,本文就不再科普FinFET晶体管结构,以及Fin Pitch、Gate Pitch、CPP、不同金属层的基本概念了。对这些内容感兴趣的同学,可阅读《为什么说Intel的10nm工艺比别家7nm更先进?(上)》,里面有比较详细的科普。

下面这两张图表给出的数据分别来自Scotten Jones(IC Knowledge,via Semiwiki)和David Schor(WikiChip Fuse)。下图综合了三星、台积电已公开的信息,以及针对现有公开信息的一些分析。

来源:Scotten Jones, IC Knowledge via SemiWiki[1],发布于2019.5

来源:David Schor, WikiChip Fuse[2],发布于2020.3

这其中值得一提的主要是晶体管密度(Transistor Density),此处IC Knowledge预计台积电N5工艺的密度为173.1 MTr/mm?(百万晶体管每平方毫米,特指逻辑电路HD高密度单元库),WikiChip Fuse此前预估数字则为171.3 MTr/mm?[2]。

IC Knowledge预计三星5LPE工艺的晶体管密度(UHD超高密度单元)126.5 MTr/mm?,WikiChip则预估为126.89 MTr/mm?[3]。

台积电N5逻辑电路1.84倍晶体管密度提升,与同功耗水平下15%速度提升

虽然有区别,但量级上差不多,台积电N5还是比三星5LPE要高出不少的(Scotten Jones在2019年年末又更新过一次晶体管密度预估,似乎又大了不少[4])。无论如何,这一点也能看出台积电和三星的5nm虽然都叫5nm,但跨步幅度还是很不一样。

另外在CPP(contacted poly pitch,栅间距)、M2P(Metal 2 Pitch,金属间距)这样的晶体管关键数值上,大神们预估的值也有一些差异,IC Knowledge标台积电N5工艺的CPP是50nm,WikiChip则估算为48nm;而M2P,IC Knowledge后来又将其更新到了28nm。这两张表格仅供参考——注意其发布时间也有差异。

事实上,三星5LPE与上一代7LPP相比,就单个晶体管的关键参数来看,各部分是几乎没有变化的,晶体管密度提升依靠的主要是单元库变化,以及各种scaling booster方法(比如SDB)。

台积电N5可不是这样。此处未详细列出N5相比N7的晶体管各部分关键参数变化。从WikiChip提供的数据来看,CPP间距N7为57nm,N5则为48nm;MMP则从40nm缩减到了30nm[5]。这也进一步佐证了三星5LPE属于7LPP的同代加强或过渡,而台积电N5是N7的完整迭代。

骁龙888“翻车”都是5nm的锅吗?

很多人说高通被三星坑了,这话大抵上是站不住脚的,或者其功耗表现不佳并不只是三星的锅。芯片设计12-18个月周期,在前期定义配置时,选择的制造工艺就已经定下来了,如今设计与制造的紧密程度是相当之甚的——且当代工艺差异,也不大可能在芯片设计阶段中途突然就转到另一种工艺上。

高通骁龙888选择三星5LPE工艺,必然是有自己的考量的。高通也绝对不可能不知道,前文提到5LPE与N5工艺这些最基本的差异。至于高通的考量究竟是制造成本本身,还是设计IP的迁移便利性,就不得而知了。或许将来TechInsights的深度拆解能探索一二。

此前的文章里提到过,这些晶体管密度数字只具有参考价值。一方面在于不同时代计算晶体管密度的方法是有差别的,这在《为什么说Intel的10nm工艺比别家7nm更先进?(上)》一文中就已经详细提过了。而且一颗芯片上,晶体管并不是只有逻辑电路,更非仅采用HD高密度单元,晶体管也不是均匀分布。具体的仍要看芯片本身的设计。

在IEDM上,台积电提到对于包含60%逻辑单元、30% SRAM,以及10%模拟I/O的移动SoC而言,其5nm工艺能够缩减芯片35%-40%的尺寸——这样的值是更具参考价值的。

至于工艺迭代或增强,对性能、功耗产生的具体影响,厂商公布的数字恐怕是很难验证的。后文会提到三星5LPE通过引入6T UHD单元、减fin以减少单元高度的方式来实现晶体管密度33%的增加。它对性能带来的影响也很难考证,或者我们这些业外人士也无法搞清楚,这种方案究竟是好还是不好。

去年在上海举办的Exynos芯片发布会上,三星有提到5LPE令芯片面积降低35%,功耗效率提升20%,性能表现提升10%。台积电则针对N5的功耗和性能数字提过,同功耗下速度提升15%,同性能下功耗降低30%。这些数字的意义可能都并不大,尤其在面对各种不同的IC设计时。

举个例子,骁龙888的CPU部分,大核心Cortex-X1。Cortex-X1是Arm的Greek家族CPU架构,它与当时一同公布的Cortex-A78在设计理念上就有较大差异。通常移动CPU更看重低功耗,并且要在功耗、性能与面积(PPA)之间达成平衡,功耗与能耗比更是每年Arm升级IP的重点。

但Cortex-X1是打破了这种传统的。其设计指针更偏向性能,且在功耗、面积方面有一定妥协。X1架构有了明显拓宽,在A78设计基础上,再加包括前端5-wide解码宽度,renaming带宽最高每周期8 Mop,NEON加倍,L2、L3 cache加倍等。Mop cache条目加倍,甚至比Intel Sunny Cove(十代酷睿)还要大。

比较具有代表性的是Re-order Buffer(ROB)增加到224条目,此前是160,以提升指令乱序与并行度。以前Arm在这方面是一直偏保守的。Arm以前曾提过,ROB拓宽带来的性能提升,与芯片面积增加,两者关系不呈线性,而且还需要以功耗为代价。Cortex-X1显然已经看破这些了。更多有关Cortex-X1的架构拓宽,不是本文要探讨的重点。

虽然论架构宽度,Cortex-X1的基础设计还是没法和苹果Firestorm(M1与A14)比,但Cortex-X1面向芯片制造商开始采用一种“Cortex-X Custom Program”授权计划。这种授权方式下,客户可以对微架构做进一步定制,比如说要求更大的ROB、改进的prefetcher等。我们不知骁龙888针对Cortex-X1的具体实施,不过它以性能为更高优先级的设计,致骁龙888产生不对等的功耗,设计与IP也是重要因素。

Arm在此前发布Cortex-X1时大力宣传了其IPC及性能提升,但对功耗和面积效益语焉不详。AnandTech猜测,X1面积和功耗都可能是A78的1.5倍;在预设功耗(power)下,X1核心的能效(energy efficiency,每焦耳的性能)会比A78糟糕23%[6]。

当然我们不能就此认定,骁龙888峰值性能下的功耗与能效比都是Cortex-X1的问题,而且Cortex-X1设计原则本身就是如此。骁龙888涉及到的问题可能覆盖了Arm、高通、EDA工具厂商,以及三星foundry。何况骁龙888 GPU部分的Adreno 660针对上代改进(提频)也比较仓促。单纯说骁龙888的功耗问题需要三星5LPE工艺背锅,显然是不靠谱的。

至于很多人说5nm“集体翻车”,前文谈到了台积电N5工艺与三星5LPE差异较大,演进方向也不同。而将5nm一概而论,以骁龙888和麒麟9000为例来说“这一代工艺都不行”更是无稽之谈。在麒麟9000的GPU IP上,Arm为Mali G78设计,堆至多24个核心原本就相当令人困惑。

即便要说台积电N5工艺“翻车”,或者三星5LPE“翻车”,这两辆车“翻”的姿势和方向应该也有很大差异。

最后提一提后续改进版工艺,三星方面自然就是4LPE了,而台积电则为N5P。4LPE的晶体管和大部分基本思路都与5LPE一致,不过金属互联间距有进一步的缩减;而台积电的N5P与N5有着相同的设计规则,完全的IP兼容性,同功耗下7%性能提升,同性能够下15%功耗降低。