革命性突破!Cadence新一代系统动力双剑为IC设计创造“芯”动力

2021-06-30

作者:韦肖葳

来源:电子技术应用

2021年6月9日,Cadence新一代硬件验证产品发布会在京举办。最新发布的Palladium Z2企业级硬件仿真加速系统和Protium X2企业级原型验证系统基于下一代硬件仿真核心处理器和Xilinx UltraScale+ VU19P FPGA,这一全新的系统为当前数十亿门规模的片上系统(SoC)设计提供最佳的硅前硬件纠错效率和最高的软件调试吞吐率。

作为一家做EDA软件起家的公司,Cadence一直以来的核心竞争力是做计算型软件。不过随着行业的持续发展,Cadence意识到客户的需求远超公司原先的设定,进入到一个新的领域,即——“系统”。目前,Cadence的整体战略思维就集中在智能系统设计上。

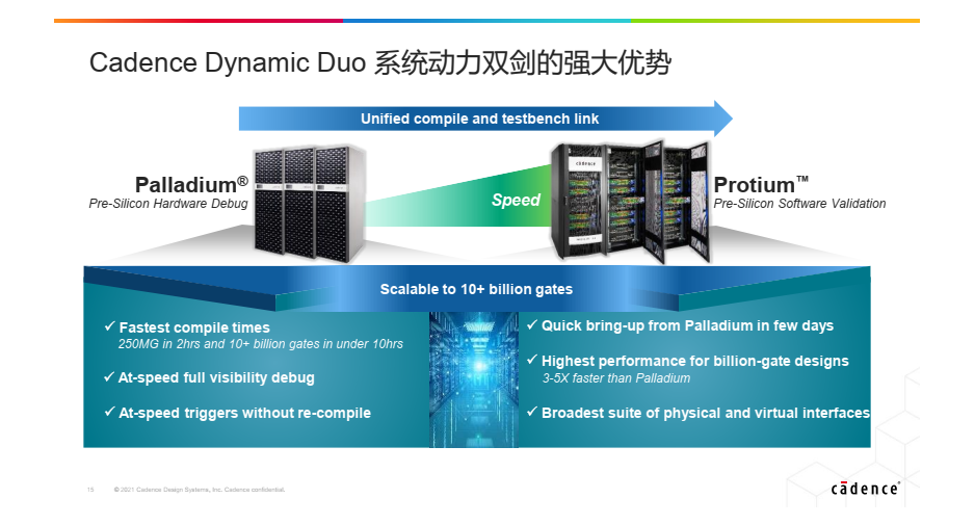

为了加速设计周期、提升算力、增强软硬件协同,Cadence提出了两个思路:第一,通过硬件的方式加速仿真;第二,引用原型验证的方法。基于此,Cadence推出了Palladium Z2和Protium X2系统动力双剑(dynamic duo),即Palladium® Z2企业级硬件仿真加速系统以及Protium™ X2企业级原型验证系统。对比2015年推出的第一代,此次全新的系统动力双剑组合基于下一代定制化的硬件仿真核心处理器和Xilinx UltraScale+ VU19P FPGA,将容量提高2倍,性能提高1.5倍。以更少的时间为大规模芯片验证完成更多次数的迭代。

在AMD全球院士、方法学架构师Alex Starr看来,系统动力双剑加速了芯片开发流程并优化了AMD的左移战略,这是AMD成功的重要成果之一。Xilinx关键应用市场资深总监Hanneke Krekels也认为,系统动力双剑的应用可以让软件工程师将宝贵的时间用于设计验证和软件开发,而非耗时的原型验证初启。

在正确的时间和使用场景中使用正确的工具

“为什么Cadence用于仿真验证有两个硬件产品呢?事实上在项目的不同时间节点所使用的工具是不一样的。在前期RTL验证、功耗分析这段时间,会使用仿真加速的方式,当80%、90%的设计都已成熟的时候,软件团队开始介入,就会慢慢将设计迁移到原型验证平台,直到最后芯片Tape Out。这种流程会让流片成功率大大提升。” Cadence亚太区系统解决方案资深总监张永专先生表示。

Cadence亚太区系统解决方案资深总监 张永专先生

Cadence在新一代产品上做了哪些升级?

制程

第一个升级是在Palladium Z2的制程上。“我们在制程上有一些新的进展。”张永专说道,“简单来说就是未来我们的仿真器可以做到几乎跟软件仿真是一样的功能。我们做了一些特殊的设计,可以让原来的硬件仿真,我们叫2 State,0跟1之外,可以加入叫4 State,这个是一个非常先进的一个做法,能够让系统兼容效率更好一点。”

FPGA

第二个突破点则是在Protium的FPGA上。据悉,Protium X1使用的是Xilinx UltraScale440,而新一代则应用了VU-19P。这使得单克容量变大,同时效能也有显著提升。“我们在整个跟主机的接连这部分,接口做了一些很大的改进,可以跟Palladium Z2这个硬件加速兼容,也就是说在硬件加速可以跑这样的一个设计,很快也可以迁移到Protium来。”张永专讲到,“所以想象一下,以后软件仿真,硬件加速,原型验证,未来可能合成一体,Compile完全是同一个平台。”

系统动力双剑,因何独霸一方?

快

据张永专介绍,Palladium Z2是目前全世界业界里编译速度最快的,能够达到数十个Billion Gate。“我可以在十个小时内就拿到Compile。”张永专说道,“早上去上班,晚上下班之前就可以拿到,每两个小时可以Compile 250 Million Gate。”

全面的纠错(Debug)功能

Debug的能力实际上取决于两方面,一个是可观测性(Visibility),另外一个就是可控制性。与基于FPGA的仿真器有所不同,基于处理器的仿真器的优势就在于Debug。Palladium Z2在设计上较为特殊,不同于商用处理器,Palladium Z2使用的是Cadence全新的自定制处理器,因此具有强大的Debug功能。“当你的设计进到Palladium这个机器之后,我们的编译器会把你的设计,再将我的排程工具转化成我的指令级,放到我这里来执行,所以我一Compile,马上就可以运行,不需要Place & Route。当你的Design放到我的Palladium里面的时候,所有的讯号我都看得到,所以准确率是100%。”张永专介绍到。

不需要重新编译

当想要在Debug过程当中触发一些条件来侦错(即:Trigger Condition)时,不需要重新编译。这一点就意味着可以通过快速迭代的方式,让设计收验,达到较好的质量。

可快速迁移

Palladium可以快速迁移到Protium,可能在几天之内就可以达到原型验证的平台。这项工作以往是需要投入很大的时间成本和人力成本才可实现的。

为10亿门芯片设计提供最优的硅前验证表现

据介绍,Protium的速度是Palladium的3-5倍。在Arm公司设计服务资深总监Tran Nguyen看来,系统动力双剑的使用使Arm在最新设计上实现了超过50%的性能提升和2倍的容量增加,为其提供了验证下一代IP和产品所需的强大的硅前验证能力。

应用层面广阔

“Protium也提供了所谓的In-circuit Emulation, Virtualization(虚拟原型), Memory Model。”张永专说道,“意味着你可以用实体的卡在上面跑,比方说PCIe,或者是虚拟的PCIe在上面跑,再或者虚拟的模型都可以。所以应用的层面非常广。”

Palladium,让硬件加速惠及整个产业

“目前整个业界的使用状况是——全球大概有90%的客户都应用了Palladium。它有最快的硅前Performance,它有强大的功能,像这样一个机架可以容纳144个用户同时在上面上线使用。”张永专讲到。据悉,Palladium可以支持所有的硬件设计,RTL Design、Verilog、VHDL都可以接受。另外,Palladium也可以跟外界的虚拟模型放在一起,可以跟仿真一起同时仿真,看起来就像软件仿真一样。此外,Palladium提供非常丰富的内存模型(Memory Model),例如:DDR5、DDR4、 HBM或UFS。 Palladium有一个特殊的模拟方式,可以把内存直接放到硬件加速器上,因此可以解决所有在复杂系统上用得到的内存模型。最后,Palladium为PCIE、USB、Ethernet等标准界面都提供相应的物理接口,例如降速墙或虚拟模型。“就目前看来,我们现在还没有任何一个设计说不能上Palladium,它可以让整个产业都能够得到硬件加速的好处。” 张永专如是说,“另外,Cadence对中小客户也会提供很好的支持,例如使用云、租用等比较灵活的方式为有资金问题困扰的企业创造更为便利的条件。”

提速安全两不误

谈及信息安全问题,张永专表示,系统动力双剑在信息安全方面同样提供保障。Cadence Palladium与服务器和主机的沟通通道是经过加密的。所以,从整体来看它的需求是不容易被破解的。由于其设计是经过编译的,并非原来的,因此使用这样的平台来进行仿真加速以及原型验证可以实现提速与与获得信息安全保障的双赢。

孪生兄弟双引擎,联手解决产业痛点

在英伟达,对高端图形和超大规模设计的每一次升级都意味着复杂性的增加,上市时间也会愈发紧张,而采用结合Cadence Palladium Z2和Protium X2系统的通用前端流程,英伟达可以优化功能验证(verification)、功能确认(validation)和硅前软件初启的工作负载分布,按时完成对最复杂GPU和SoC设计的全面验证。“这两个系统动力双剑像孪生兄弟双引擎,协助解决整个产业现在看到的比较大的问题。”张永专最后总结道。