FPGA教学——如何自动产生一个UVM环境

2022-08-11

来源:FPGA之家

之前有朋友问我怎么用脚本产生一个验证环境,这个问题今天和大家介绍下两种做法。

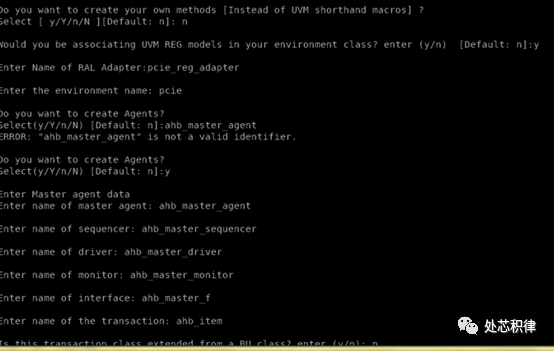

第一种用VCS自带的uvmgen工具

当你在命令行时直接输入uvmgen会输出如下信息

选择1

然后按照提示步骤进行UVM环境的创建

创建完之后我们看看环境目录

刚才我们创建的env,agent,scoreboar,coverage收集模块等都已经完备,跑环境的Makefile也都自动生成好了。对于一些简单的UVM环境,用uvmgen还是非常适用的。

但是采用这种方式产生UVM环境的局限也比较明显,比如agent不能添加多个等,对于一些复杂的验证环境还得自己手动添加。有没有一种脚本能够将整体框架大家好,甚至将验证管理中的checklist都准备妥当。下面介绍的这个uvmdvgen.py 脚本将实现这些强大的功能。

介绍下这个脚本实现的功能

可以快速生成 agent;

能够根据用户需求产生UVM环境;

自带checklist;

自带testplan;

这里产生的UVM环境可以支持多个不同的agent,并且UVM环境的编码风格对复用性非常友好。让我们看看这款UVM的脚本是怎么使用的。

用-a 单独生成一个agent,例如

uvmdvgen.py i2c -a

生成i2c 的agent

用-s 可以一个agent里面增添 host driver 和device driver

uvmdvgen.py i2c -a -s

讲完agent,开始讲environment,用-e 产出UVMenvironment

uvmdvgen.py i2c -e

Checklist,Testplan,UVMenvironment 一应俱全。

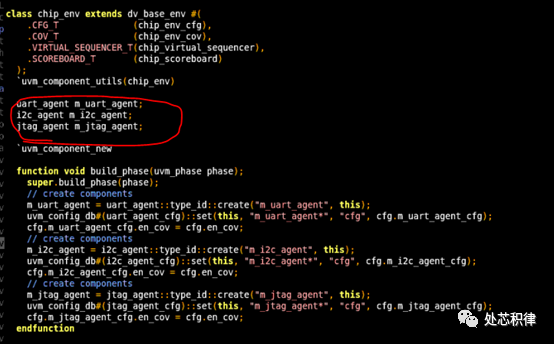

用-ea添加agent,可以随便添加多少个agent

uvmdvgen.py chip -e-ea uart i2c jtag

如此在environment添加agent便完成了。

该脚本还可以用-hi和-hr实现是否有interrupt,register model等功能。

是不是功能超级强大,迫不及待想用这个脚本的小伙伴可以在下面链接获取。

https://github.com/lowRISC/opentitan/tree/master/util/uvmdvgen

更多信息可以来这里获取==>>电子技术应用-AET<<