入门:Xilinx SRL16E如何实现16移位寄存器

2022-08-30

来源:FPGA设计论坛

在做FPGA的开发过程中经常会使用到移位寄存器,一般我们使用移位寄存器的目的都是为了将某个信号进行打拍,使得时序符合我们的需求。最常见的一种打拍方法就是在process过程语句中对信号进行移位(在verilog中是在always过程中进行移位)。但是这里我给大家介绍一下SRL6E,这个是Xilinx提供的一个原语,顾名思义,这是一个可以最大实现16位移位寄存的移位寄存器。

需要注意的是,SRL16E原语在不同的器件中表现形式可能稍有区别,下面是在Kintex-7系列器件中的SRL16E原语:

--使用原语时,需要加上这两句

Library UNISIM;

use UNISIM.vcomponents.all;

-- SRL16E: 16-bit shift register LUT with clock enable operaTIng on posedge of clock (Mapped to SliceM LUT6)

-- Kintex-7

-- Xilinx HDL Language Template, version 2017.4

--以下时=是SRL16E原语

SRL16E_inst : SRL16E

generic map (

INIT => X“0000”)--对寄存器进行初始化

port map (

Q => Q, -- SRL data output--寄存器输出端口

A0 => A0, -- Select[0] input--四个地址输入端口

A1 => A1, -- Select[1] input

A2 => A2, -- Select[2] input

A3 => A3, -- Select[3] input

CE => CE, -- Clock enable input--寄存器使能端口

CLK => CLK, -- Clock input --时钟端口

D => D -- SRL data input--寄存器输入端口

);

-- End of SRL16E_inst instanTIaTIon

这里主要对地址进行一下说明。地址A3A2A1A0表明要对输入数据进行多少移位。如果是A3A2A1A0=“0000”,说明是对D端口输入数据进行1位移位,也就是说对D端口输入的数据进行一个周期的延迟。如果是A3A2A1A0=“1111”,说明是对D端口输入数据进行16位移位。

下面举一个例子来说明:

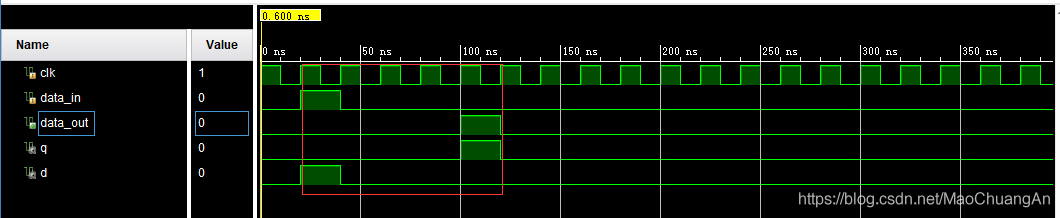

这是源程序,因为A3A2A1A0=“0011”,所以主要是对输入数据进行4个周期的延迟。

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 2018/12/10 1605

-- Design Name:

-- Module Name: srl16e_test - Behavioral

-- Project Name:

-- Target Devices:

-- Tool Versions:

-- DescripTIon:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

Library UNISIM;

use UNISIM.vcomponents.all;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity srl16e_test is

Port (

clk : in std_logic;

data_in : in std_logic;

data_out: out std_logic

);

end srl16e_test;

architecture Behavioral of srl16e_test is

signal q : std_logic:='0';

signal d : std_logic:='0';

begin

SRL16E_inst : SRL16E

generic map (

INIT => X“0000”)

port map (

Q => q, -- SRL data output

A0 => '1', -- Select[0] input

A1 => '1', -- Select[1] input

A2 => '0', -- Select[2] input

A3 => '0', -- Select[3] input

CE => '1', -- Clock enable input

CLK => clk, -- Clock input

D => d -- SRL data input

);

d <= data_in;

data_out <= q;

end Behavioral;

这是仿真文件:

仿真文件中的输入数据是一个周期的单脉冲。

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 2018/12/10 1615

-- Design Name:

-- Module Name: tb_srl16e - Behavioral

-- Project Name:

-- Target Devices:

-- Tool Versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

use IEEE.STD_LOGIC_ARITH.All;

use IEEE.STD_LOGIC_UNSIGNED.All;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

library UNISIM;

use UNISIM.VComponents.all;

entity tb_srl16e is

end tb_srl16e;

architecture Behavioral of tb_srl16e is

component srl16e_test

port(

clk : in std_logic;

data_in : in std_logic;

data_out : out std_logic

);

end component;

signal clk ='1';

signal in_data : std_logic:='0';

signal out_data: std_logic:='0';

begin

uut: srl16e_test

port map(

clk => clk,

data_in => in_data,

data_out => out_data

);

process

begin

wait for 10 ns;

clk <= '0';

wait for 10 ns;

clk <= '1';

end process;

process

begin

in_data <= '0';

wait for 20 ns;

in_data <= '1';

wait for 20 ns;

in_data <= '0';

wait;

end process;

end Behavioral;

仿真波形:

输入数据是data_in,输出是data_out,可以看到对输入数据进行了4个周期的延迟。

更多信息可以来这里获取==>>电子技术应用-AET<<