入门:基于硬件描述语言HDL的FPGA开发

2022-09-28

来源:CSDN

FPGA是一个很特殊的芯片,可能在2个月前,我还对它一无所知。我们熟知的芯片都是CPU,GPU,或者知道ASIC的概念。但实际上,FPGA已经走过了30个年头,它目前已经成为一个包含各种先进电路,逻辑单元,接口,芯片封装,制造等技术的“集大成者”。在硬件不断发展的同时,FPGA的开发软件和设计工具也在不断迭代和更新。基于硬件描述语言HDL,抽象出HLS(High-Level Synthesis)(翻译为高层次综合?怎么听起来都沉得别扭)技术,通过高层设计去隐藏很多底层逻辑和细节,让FPGA的开发更加简单。即使这样,FPGA开发还是同CPU,GPU不一样,它需要设计者在一定程度上了解FPGA的内部架构,这样才能引导高层语言综合工具睡时到优化的系统性能。

一:开发FPGA的痛点

首先,FPGA的体量非常大,大得惊人,英特尔最新的StraTIx10 GX 10M 有 433亿只晶体管,1020万个可编程逻辑单元,以及2304个可编程的I/O接口。这些数量庞大的晶体管组成了大量的可编程逻辑单元和查找表结构,大量运算单元,各种类型和大小的内存资源,高速串行I/O,多个嵌入式处理器,还有成百上午种不同功能的软核和硬核IP。因为可编程,可以通过定制实现极高吞吐量和极低的功耗。

当这么多硬件资源都集成到了一个芯片上,用户如何对这些硬件进行编程呢?

通常来说,我们要解决一个复杂问题,常用的办法就是分解任务,我们需要划分清楚哪些是在硬件上完成,哪些通过软件完成。在FPGA,这种分解非常困难和复杂。例如:哪部分用编程逻辑(硬件),哪部分使用片上的芯片。如何合理分配片上内存,内不足时,如何优化……

如何降低FPGA的开发难度,EDA软件一定要好用,所以,不管英特尔还是赛灵思,包括我了解的一个新创团队,都会在EDA软件团队上做大力投入,甚至做EDA软件开发的人员要多于FPGA本身的工程师数量。另外,业界也出现了大量的第三方公司,负责FPGA设计咨询公司,IP提供商,外包公司等……,业务已经发展产生了很多特定的分工。

当前,FPGA还在进入更多的市场,比如:嵌入式应用,5G和汽车市场,这些领域中的大多数开发团队都没有FPGA相关的设计专业知识和经验。而且,他们更多是纯软件开发,更多依赖于人工智能技术。这些也使得FPGA的开发难度被放大。

二:HLS——让软件工程师开发FPGA

HLS指的是通过EDA工具,将描述的逻辑结构转换成低抽象级语言描述的电路模型的过程。

这里,我不得不再强调一下HLS的概念,因为记不住,搞不太懂。

High-Level Synthesis 简称:HLS 指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。有点象我们软件领域讲的 Java 语法在运行时,根据不同的机器翻译成不同的机器字节码。所谓高层次语言,通常指的是 C,C++,SystemC等,通常有点较高的抽象度,并且往往不具有时钟或时序的概念,相比之下,诸如Verilog,VHDL,SystemVerilog等低层次语言,通常用来描述时钟周期精准的寄存器传输级电路模型,这也就是当前ASIC或者FPGA设计最为普遍使用的电路建模和描述方法。

为什么要使用HLS?

1: 这是一个趋势。因为集成电路的复杂度太高,已经逐渐超过人类可以手工管理的范畴。使用RTL代码,代码行过多,不现实。而使用C,C++ 等高层语言,可以将代码缩至10%。

根据NEC2004年发布的研究,一个拥有100万逻辑门的芯片设计通常要编写30万行RTL代码。

2: 高层语言更善于复用,特别是对于IP的重用。

因为传统的RTL的IP 往往需要定义固定的架构和接口标准,在IP重用时,需要大量的时间运行系统互联和接口验证。高层语言屏蔽了这些要求,转而由HLS工具具体来负责完成。现代FPGA有大量的IP单元,这些IP有固定功能,一定需要大量复用。

3: HLS能帮到软件和算法工程师参与主导芯片设计,这是因为HLS能够屏蔽实现细节。对于硬件工程师,HLS也能帮助他们快速设计迭代,专注于性能,面积或功耗模块,不用关注上层的算法实现。

我们在谈HLS前,先看看RTL的发展:

通过描述寄存器到寄存器之间的逻辑功能描述电路的HDL层次。RTL级是比门级更高的抽象层次,使用RTL级语言描述硬件电路一般比门级描述简单高效得多。这个时期,工程师们都在关注RTL。

HLS经过发展,产生了以C++ 为主的目标语言,从而被很多不少不了解RTL的工程师所接受。而且,HLS在性能上也近似RTL的水平。

到现在,英特尔,赛灵思,包括多伦多大学都推出了各自的HLS工具。

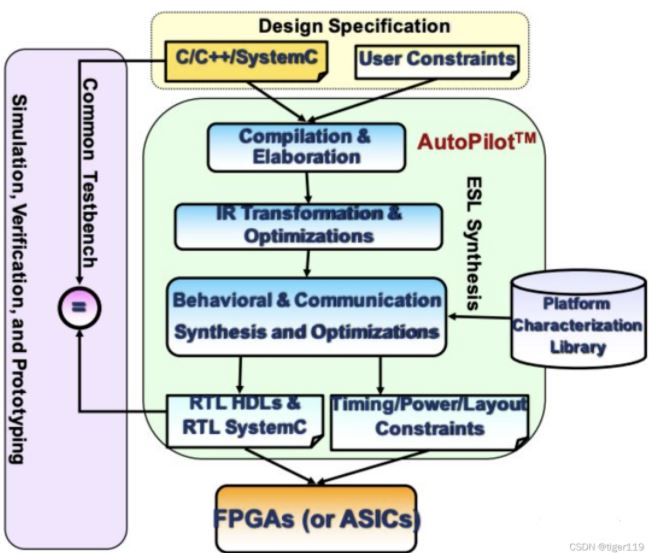

其中比较成功的工具是AutoPilot,

前端,它使用了LLVM的编译器架构,能够使用C,C++,OSCI SystemC等语言,使用llvm-gcc编译器将高层语言模型转换为IR,优化后,再根据具体的硬件平台,生成RTL代码。

AutoPilot在某些领域完胜人工优化RTL的结果。说明了HLS的潜力。

HLS的主流优化方法有以下几种:

1: 字长分析和优化。

FPGA的一个最主要特点可以使用任意字长,所以 HLS工具也不需要拘泥于某种固定的长度。好处呢,对性能提升和面积缩减有帮助。

2: 循环优化

可以使用多面体模型来达成循环优化,可以帮助实现性能和面积优化,同时也能帮助提升内存的使用效率。

3: 对并行的支持。

RTL是可以直接实例化成多个运算单元并行执行的,C/C++ 一开始是顺序执行,但后面也引入的并行支持。如:pthreads和OpenMP等多线程并行编程方法,以及OpenCL等针对GPU异桅系统进行并行编程的扩展。

作为HLS工具,一定要支持并行。比如:lgeup就整合了对pthead,OpenMP的支持。英特尔推出了OpenCL SDK,将其引和HLS,并生成FPGA硬件电路逻辑和CPU代码两部分,从而实现FPGA作为硬件加速模块的快速开发。

尽管如此,HLS要完全替代人工的RTL建模,还有很长的路要走。对于FPGA而言,内存瓶颈是制约性能的关键要素,所以,如何有效利用片上和片外的各类存储单元,是HLS的研究热点。

P4 语言是实现SDN 的重要手段,所以,新型的FPGA开发工具,需要对P4进行编译和支持。

三:商业级的开发工具

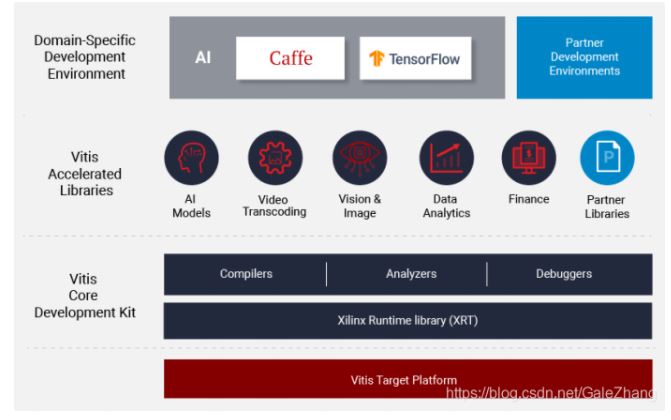

3.1 赛灵思ViTIs 开源开发工具

ViTIs花费了 1000人。年的开发工作量。

ViTIs的核心架构示意图如下:

3.2 英特尔oneAPI

OneAPI 可以针对英特尔的所有芯片进行编程。

英特尔将旗下的芯片分成了SVMS四类:

标量架构(Scalar):CPU

矢量架构(Vector):GPU

短阵架构(Matrix):AI芯片

空间架构(Special): FPGA.

四:业界看法

业界普遍认为,GPU之所以在人工智能获得成功,很大程度上取决于对软件和算法工程师的友好。而FPGA虽然在不断扩展应用范围,在性能和功耗上也不比GPU差,但是,它的编程仍然是以RTL开发为主,这对开发者并不算友好。

所以,FPGA在HLS上的发展和突破,可能是FPGA能否有更广泛应用的最后一块拼图。

更多信息可以来这里获取==>>电子技术应用-AET<<