三星与SK海力士竞逐3D DRAM 争夺AI时代内存主导权

2026-05-08

来源:IT之家

5 月 8 日消息,科技媒体 Wccftech 昨日(5 月 7 日)发布博文,报道称为突破 10nm 以下制程微缩瓶颈,三星与 SK 海力士两大巨头正研发下一代 DRAM 制造工艺,争夺行业主导权。

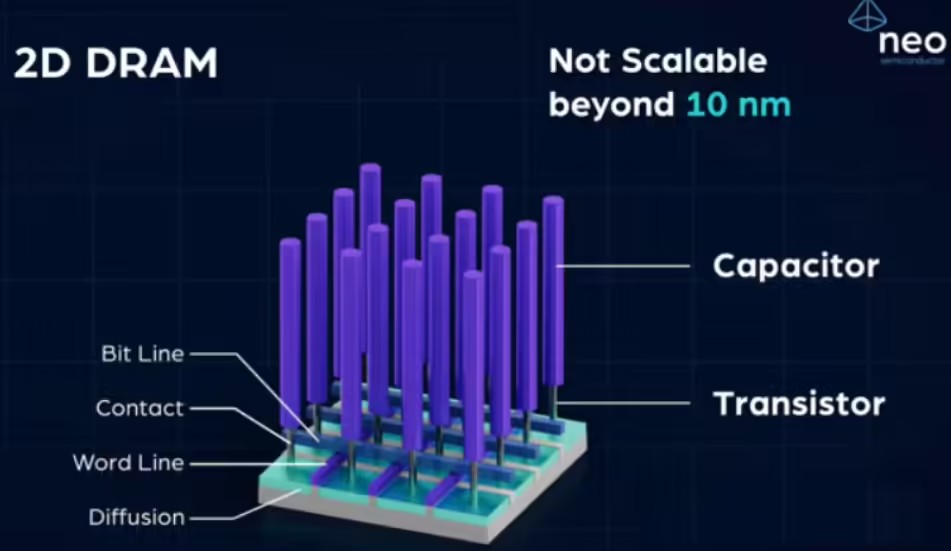

援引博文介绍,不同于处理器,DRAM 内存芯片必须依靠电容器存储数据。随着制程节点不断缩小(如 10nm 以下的 1c 节点),电容器的尺寸难以继续缩减,晶体管间距缩小也增加了短路风险。

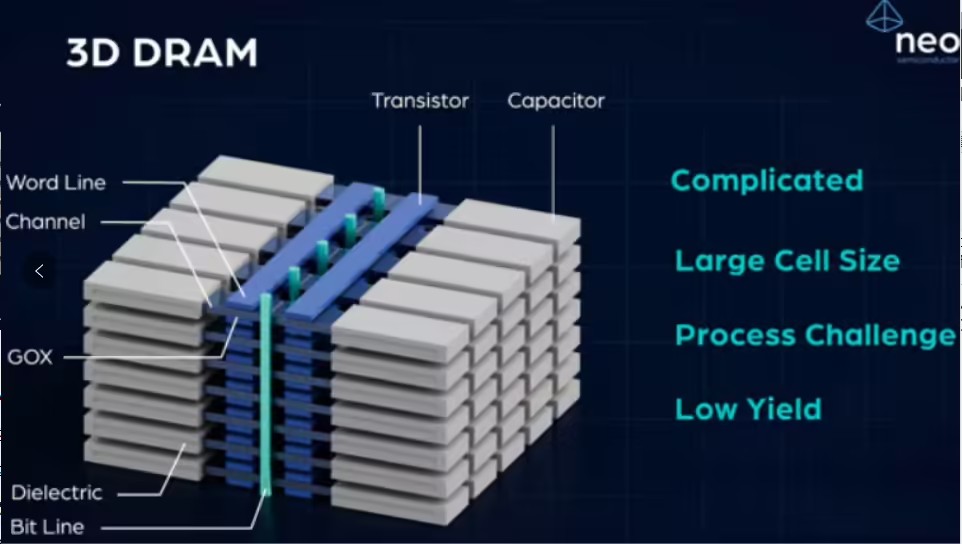

为了让密度进一步提升,行业正转向 3D DRAM,将传统 2D 平面排列的 DRAM 单元改为垂直或立体堆叠架构的内存技术。其原理类似 3D NAND 闪存,通过改变晶体管排列方向(如水平放置)或垂直堆叠,在缩小制程时保持电容器容量。

不过在技术实现方面,三星和 SK 海力士已分化出不同发展路线。

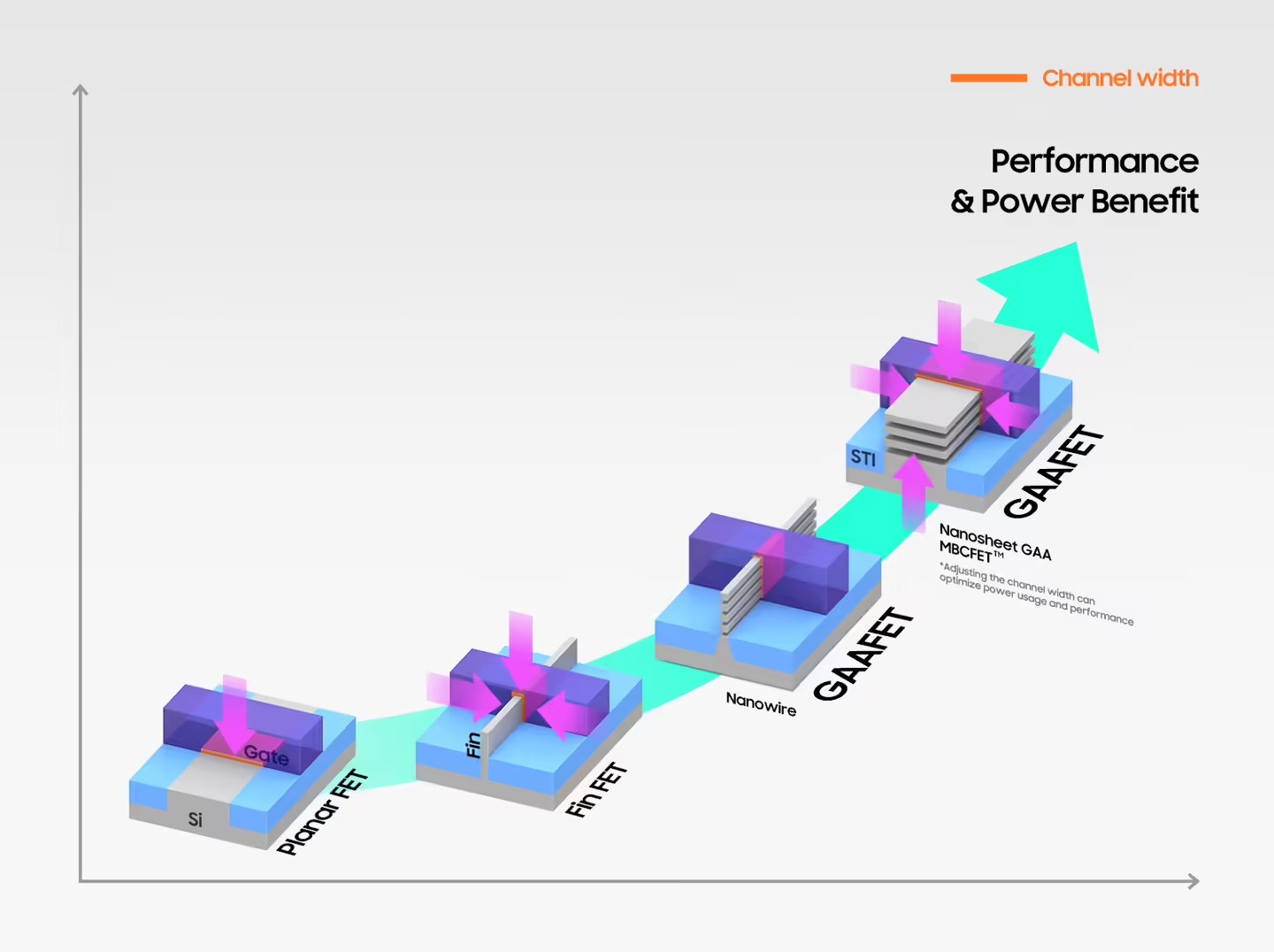

三星方面计划推广 GAAFET 工艺。在处理器制造中,GAAFET 通过栅极包裹沟道来提升电流控制力;但在 DRAM 中,三星必须将 GAAFET 晶体管与电容器整合在同一单元内。为此,三星考虑借鉴 NAND 闪存的设计,把负责读写操作的控制电路置于存储阵列下方。

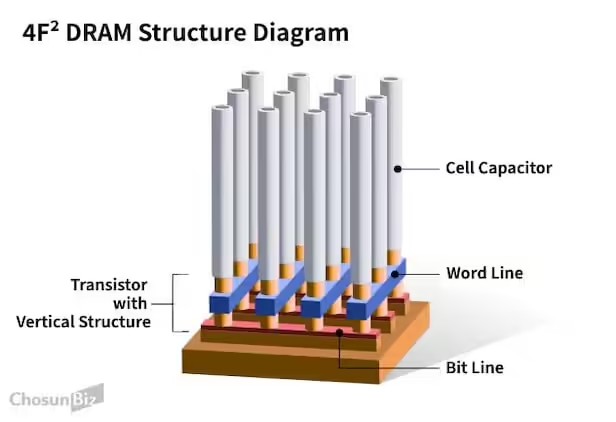

而 SK 海力士选择了 4F2 架构。该方案将晶体管垂直堆叠,同样用栅极材料包裹晶体管,而接收电容数据的组件则置于晶体管柱下方。这种结构与 GAAFET 有相似之处,但空间布局逻辑截然不同。

该媒体指出两大巨头路线分化,核心目标一致:率先实现技术量产,推动自家方案成为下一代 DRAM 的行业标准。谁能率先跑通工艺并提升良率,谁就能在 AI 时代的内存市场占据主导。

TSMC 2nm 芯片示意图

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。