利用异步采样电路提高SRAM工艺FPGA的设计安全性

2008-05-07

作者:陈文涛, 金德鹏, 曾烈光

摘 要: 提出了一种利用外接CPLD提高SRAM工艺FPGA设计安全性的方法。该方法利用异步采样电路的不确定性生成随机序列,并且每次上电" title="上电">上电都产生不同的随机序列,断绝了剽窃者通过克隆序列对系统进行破解的可能性。此外,芯片之间通信采用了M序列加密,以进一步增强系统的安全性。

关键词: SRAM工艺FPGA 设计安全性 异步采样电路 M序列

随着FPGA的容量、性能以及可靠性的提高及其在消费电子、汽车电子等领域的大规模应用,FPGA设计的安全性问题越来越引起人们的关注。相比其他工艺FPGA而言,处于主流地位的SRAM工艺FPGA有一些优势,但是由于SRAM的易失性,掉电以后芯片中的配置信息将丢失,所以每次系统上电时都需要重新配置。这就使得剽窃者可以通过对FPGA的配置数据引脚进行采样,得到该FPGA的配置数据流,实现对FPGA内部设计电路" title="设计电路">设计电路的克隆。为了保护设计者的知识产权以及推动SRAM工艺FPGA更大规模的应用,产业界和学术界从加密算法的角度对SRAM工艺FPGA的设计安全性提出了多种解决方案[1~2]。

异步电路的竞争和险象问题所导致的不确定性,是数字电路设计中令人头疼的问题。但是,如果把这种不确定性应用在本安全方案中,同样可以困扰剽窃者,从而更有效地保护设计。为此,本文提出了利用异步采样电路的不确定性提高SRAM工艺FPGA设计安全性的方法,以提高系统的安全性。

1 方案简介

1.1 设计方案的指导思想

(1) CPLD是难以用反向工程等物理手段进行破解的,而且用这些方法破解CPLD的成本和设计的开发成本相近。Xilinx公司声称其CoolRunner-II系列CPLD的安全性完全可以达到ASIC相当的等级[3]。并且,CPLD也可以用抗攻击性强的小规模反熔丝FPGA来代替[4]。

(2) CPLD中触发器资源较少,因此应尽量降低CPLD中的电路复杂度。

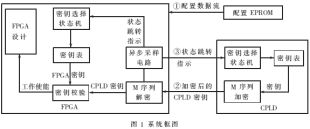

本方案借助了跳频的理念,在FPGA和CPLD中分别保存两个密钥表,在一开始同步之后,FPGA中的密钥选择状态机根据异步采样电路输出的状态跳转指示信号进行跳转。同时CPLD接收FPGA送来的状态跳转信号,其中的密钥状态机也进行相应的跳转,并将密钥传回给FPGA。在没有差错的情况下,这两个状态机将一致地跳转。FPGA通过对CPLD送来的密钥进行确认来验证CPLD的合法性:检验是否和自己的密钥状态机所选择的密钥一致,如果一致,则说明所连接的CPLD为合法的CPLD,FPGA电路正常工作;否则认为所连接的CPLD为非法,停止FPGA电路工作。由以上指导思想设计的系统框图如图1所示。

此外,CPLD向FPGA传递的密钥先利用M序列进行加密,这样使得对系统的破解首先需要对M序列加密算法进行破解,从而进一步提高了系统的抗攻击能力。

1.2 异步采样电路

温度的变化、电压的波动等因素都会使晶振所输出的时钟发生抖动。因此,用一个时钟去采样另一个时钟驱动的信号,其采样值是不可预测的。异步采样电路的机理就是利用两个时钟之间相位和频率的不确定性,产生一个不可预测的序列。单比特异步采样电路的示意图如图2所示。图中有4个触发器(FF1、FF2、FF3、FF4)和两个时钟(clk、clks)。FF1、FF2由clks信号驱动,其中FF1是用于防止亚稳态出现的触发器,它的输入信号同步于clk的信号,FF2的输出信号则同步于clks的信号。FF3、FF4由clk信号驱动,其中FF3的作用和FF1类似,用于防止亚稳态的出现,它的输入信号同步于clks的信号;FF4的输出信号则同步于clk的信号。通过上述处理后,FF4的输出产生了一个随机序列,这个随机序列不同于同步电路产生的伪随机序列" title="伪随机序列">伪随机序列,其状态的转移同温度、电压等外界因素有关,是一个完全不可预测的随机序列。此外,异步采样电路对两个时钟之间的相位敏感,所以在电路板每次上电时所生成的序列也是不同的。

异步采样模块的VHDL实现如下:

--this process is triggered by clks

process(rst, clks)

begin

if rst=‘0’ then

ff1 <= (others=>‘0’);

ff2 <= (others=>‘0’);

elsif clks‘event and clks=‘1’ then

ff1 <= din; --din is the signal triggered by clk

ff2 <= ff1;

end if;

end process;

-- this process is triggered by clk

process(rst, clk)

begin

if rst=‘0’ then

ff3 <= (others=>‘0’);

ff4 <= (others=>‘0’);

elsif clk′event and clk=‘1’ then

ff3 <= ff2;

ff4 <= ff3;

end if;

end process;

dout <= ff4; -- dout is output random signal

其中:din为同步于clk的输入序列,dout为输出的随机序列。

将本文所设计的方法应用到Altera公司的Cyclone[5]系列FPGA中,利用Quartus II中的SignalTapII Logical Analyzer工具,两次采样复位后FPGA内异步采样电路的输入输出信号,得到如图3所示的波形,其中两个时钟:clk为2.000MHz,clks为2.048MHz。观察系统复位后异步采样电路输出序列的随机性可以发现,每次将系统复位后,采用同步电路设计的伪随机序列发生器产生相同的伪随机序列(din);但是,将这个伪随机序列(din)输入异步采样电路后,在输出(dout)却得到不同的随机序列。这说明同一块电路板每次上电时都将生成不同的随机序列。

1.3 密钥选择状态机

FPGA和CPLD中各有一个完全相同的密钥选择状态机,该状态机根据异步采样电路输出的随机序列进行跳转,其跳转规则可以自定义。在本文设计的系统中,密钥表中存放有8个32位长的密钥,密钥状态机共有8个状态,记为状态0~状态7,每个状态分别对应一个密钥,记为密钥0~密钥7。

假设当前状态为状态i,异步采样电路的输出为j,其中i、j∈N,且0≤i, j≤7。那么可以采用如下简单的跳转规则:当采样电路的输出为0时,跳转到状态0;否则,跳转到状态(i+j)mod8。为了提高系统的安全性,也可以采用各种无序的跳转规则,通过改变跳转规则和密钥表,可以得到不同的系统。

1.4 M序列加密解密电路

由于CPLD向FPGA传递密钥之前,先利用M序列进行加密,使得对系统的破解首先需要对M序列加密算法进行破解,这样既防止了密钥的明文传输,又提高了系统的安全性。之所以采用M序列作为加密算法,主要考虑的是解密的自同步特性。此外根据本设计的假设即CPLD的破解是不可行的,考虑到CPLD触发器资源紧张,对FPGA向CPLD之间的跳转指示信号的传输没有进行加密,为此而节省了CPLD中的电路。

M序列的级数越大,生成的随机序列的周期越长,破解的难度也越大。这里采用20阶的M序列,其本原多项式为x20+x3+1。

1.5 密钥校验

CPLD将其密钥状态机所对应的密钥回送给FPGA,FPGA则通过对CPLD送来的密钥进行确认来验证CPLD的合法性。为了不至于多占用引脚,32位密钥是串行传输" title="串行传输">串行传输的。串行传输给剽窃者的破解也增加了难度,但同时带来的问题是:FPGA需要先进行同步和串并转换之后才能进行密钥校验。

密钥校验的状态机如图4所示。状态机共有失步" title="失步">失步、预同步、同步和保护四种状态。预同步状态的设置是为了防止假同步,只有连续三次校验正确才认为找到了同步。保护状态的设置是为了防止误码引起不必要的失步,使得偶尔的误码并不会导致校验状态机失步。下面分别介绍密钥校验电路在这四种状态的具体工作方式:

(1)失步状态:系统刚启动时,FPGA的密钥校验状态机处于失步状态,此时异步采样电路不工作,输出为0,CPLD一直发送密钥0。密钥校验电路在M序列解密电路输出的串行密钥流里搜索密钥0的码型,在搜索到密钥0的码型后,密钥校验状态机跳转到预同步状态。

(2)预同步状态:当密钥校验状态机处于预同步状态时,异步采样电路仍然不工作,输出跳转指示为0,CPLD仍发送密钥0。密钥校验电路进行密钥0校验,如果连续三次密钥校验正确,则进入同步态;否则返回失步态重新进行密钥搜索。

(3)同步状态:此时异步采样电路开始工作,输出随机序列指示FPGA和CPLD中两个密钥状态机进行跳转。此时密钥校验电路将CPLD送来的密钥和FPGA内部选择的密钥进行对比,如果发生校验错误则跳转至保护状态;否则继续进行密钥校验工作。

(4)保护状态:异步采样电路依然工作,密钥校验电路继续进行密钥校验,如果连续三次密钥校验错误则跳转到失步状态重新进行密钥搜索;否则返回同步状态。

在密钥校验电路中设有错误计数器,该计数器在失步状态下计数。一旦错误计数器的计数超过设定的阈值,则认为密钥检验失败,停止FPGA电路的工作使能。

2 安全性分析

这里列举几种常见的攻击方法,并简要分析本方案在这些攻击下的安全性。由于本设计假设CPLD的破解是不可行的,所以不考虑对CPLD进行反向工程直接破解等方法。

2.1 对配置数据流进行采样

剽窃者通过对FPGA的配置数据引脚(图1中的位置①)进行采样,得到该FPGA的配置数据流,实现对FPGA内部设计电路的克隆。

这种方法显然是不可行的,因为FPGA只有在确认了所连接的为合法CPLD以后才能正常工作,也就是说,需要同时克隆一份CPLD内的设计才能使得FPGA正常工作。

2.2 对密钥数据流进行采样

剽窃者利用2.1中所述方法对FPGA内部设计电路进行克隆以后,又对密钥数据流(图1中的位置②)进行采样,用存储器将这些密钥数据流存起来,在FPGA上电后将这个密钥数据流发送给FPGA,企图模拟一个合法的CPLD。

这种方法也是不可行的。因为异步采样电路对两个时钟之间的相位敏感,所以在电路板每次上电时所生成的随机序列是不同的,也就是说,每次上电后产生的密钥数据流是不同的。因此,经过这次采样得到的密钥数据流,下次上电时能用的可能性很小。

2.3 CPLD工作原理分析

由以上分析可以发现,本方案能够很好地抵抗克隆攻击。所以,要破解本方案,剽窃者只有同时对FPGA和CPLD之间的数据进行采样(图1中的位置②和③),根据CPLD的输入输出分析CPLD的工作原理,从算法层面上破解CPLD,但很难成功破解。因为:

(1)由于FPGA和CPLD之间的密钥数据流经过M序列

加密以后再进行传输,所以破解M序列加密算法是分析CPLD的第一步。同时加密时因采用了20阶M序列,并且每32个周期改变一下密钥,提高了序列综合进行分析的难度。

(2)有8个32位的密钥,而密钥的长度和个数对于剽窃者来说都是未知的。

(3)在破解了M序列加密算法和获得所有的密钥以后,还需要破解毫无规律的密钥选择状态机。即使一个8状态的状态机,因每个状态有8种转移的可能性,总的转移关系就有88=16 777 216种。

因此,想要破解本系统所需的精力和成本都相当高。剽窃者需要知道足够的系统设计参数,例如M序列生成多项式、密钥个数、密钥长度、密钥状态机个数以及密钥选择状态机转移规则等,才能对本方案成功破解。

对FPGA设计安全性的思考源于所采用的Xilinx公司的Spartan3系列和Altera公司的Cyclone系列FPGA进行产品的开发。本文所提出的方案是利用异步采样电路的不确定性使得系统不易被克隆。将该方案融合到其他加密方案中,可进一步提高这些方案的安全性。

参考文献

1 Xilinx Coporation. Virtex-II platform FPGA Handbook[EB/OL]. Available on www.xilinx.com,2004

2 Bossuet L, Gogniat G, Burleson W. Dynamically configurablesecurity for SRAM FPGA bitstreams[A]. In Proceedings of the 18th international parallel and distributed processing symposium[C], 2004:146~152

3 Xilinx Coporation. CoolRunner-II CPLD in secure applica-tions[EB/OL]. Available on www.xilinx.com, 2002

4 Actel Corporation.Understanding actel antifuse device security[EB/OL]. Available on www.actel.com, 2004

5 Altera Corporation. Cyclone device handbook datasheet[EB/OL]. http://www.altera.com, 2003