SDH技术是最重要的宽带传输技术,其在IP网络中应用也十分广泛,是最重要的骨干网传输链路类型,因此开发POS(Packet over SDH,SDH网上传IP)线卡成为核心路由器等高端IP网络设备开发中的重点。

在实际使用中,SDH信号有2种:一种是整体信号(concatenated mode,在其速率等级标识中以“c”结尾),这种信号直接采用高阶虚容器进行数据映射,如STM-16c信号类型的含义就是其内部帧结构是按照2.5 Gb/s的速率虚容器进行字节间插,而不是由多个低阶容器映射而得,因此无法将其明确的分为多个155 M或者622 M信号;另一种是通道化信号(channelized mode,在其速率等级结尾处没有“c”),这种信号是由低阶虚容器逐级映射而得到,因此对STM-16信号,它可通过区分帧结构内部的字节阵列来得到多个155 M信号或者622 M信号。

对应于上述2种SDH信号,在POS传输中有2类线卡,一类用于处理整体SDH信号,一类用于处理通道化POS信号,这里重点讨论后者。通道化POS线卡在目前主要网络设备供应商的产品目录里较少提及,但是其应用领域却越来越广。随着宽带接入需求的不断发展,许多企事业单位都需要租用独享的链路,通道化的 POS不仅能够满足这一要求,而且由于其对信号的汇聚能力强,因此还有节省布线资源及维护升级和线路备份成本低等优点。因此,通道化线卡的应用前景非常好,而且已经在许多特种行业中得到广泛的应用。

本文首先对通道化0C48(2.5 G)的设计需求进行分析,据此提出了基于PM5360和FPGA的整体设计方案,鉴于链路层处理器件PM5360在设计中的独到之处以及使用中的难点,论文重点分析了其使用要点和难点,并给出了能够灵活支持多种模式的芯片配置方法和软件设计。

1 设计需求分析

0C48通道化线卡的设计除需要满足通道化POS信号的处理需求外,还需要根据其可能的应用领域进一步确定,主要包括:1)能够对通道化OC48信号进行最小粒度为0C3的处理,需要支持单一OC3、单一OCl2以及混合方式,通道化0C48模式下的每个0C12能够进一步通道化为更细粒度的4个 0C3;2)兼容非通道化的0C3c、OCl2c、OC48c信号处理;3)支持上述工作模式的动态配置;4)支持IP包的线速处理。

2 整体方案

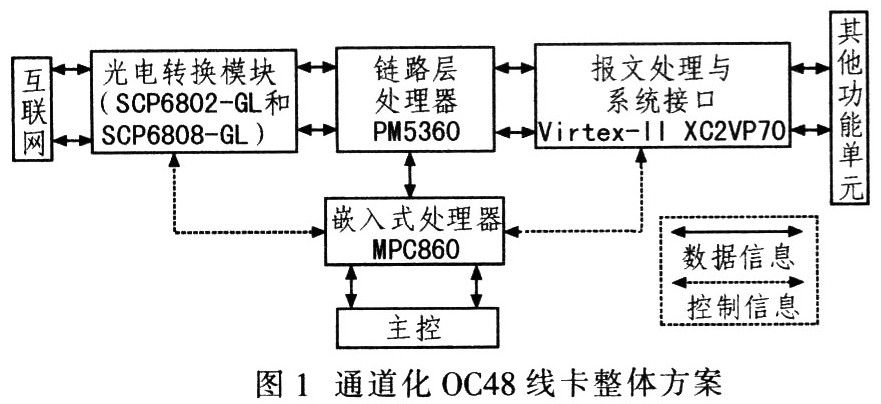

根据现代路由器等IP报文路由转发设备的结构和功能需求,图l给出了通道化0C48接口的整体设计方案。

由于需要满足支持OC-3、OC-12和OC-48 3种不同速率的POS接口,因此选用Sumitomo Eleetric公司的SCP6802-GL和SCP6808-GL 2种型号的光器件,完成光电转换功能。其中SCP6802-GL支持155 M/622M 2种POS接入速率,SCP6808-GL支持2.5 G POS接入速率,2种器件的封装兼容,且支持热插拔,可以根据接口需求方便的转换。

链路层处理是线卡要完成的关键功能,根据需求分析,这里选用PMC公司的PM5360为主处理器,该器件采用“成帧器与物理接口一体化”设计思路,将链路层处理和物理层处理功能集成在单一芯片内部。

该器件支持l路OC48,或支持总速率不超过OC48的4路OC3与0C12的任意组合,并支持接口工作模式的动态改变;根据Internet工程任务组 (IETF)PPP工作组的RFC 2615(1619)/1662,执行基于SONET/SDH规范的点对点协议(PPP):为POS或ATM应用提供SATURN POS-PHY第3层32位系统接口(时钟频率高达104 MHz),即标准的SPl3接口;支持每个传输串行流的独立环路时钟工作方式;支持从每条线路端接收流至相应传输流的独立线路环回,以及支持从线路端传输流至相应线路端接收流接口的独立诊断环回;提供通用16位微处理器总线接口,用于配置、控制和状态监控;低功耗1.8 V CMOS核心逻辑,具有3.3 V CMOS/TTL兼容性数字输入和输出功能,PECL输入与输出符合3.3 V标准。

报文处理模块采用FPGA完成,根据对资源需求的估算,选择Xilinx公司的Virtex-II XC2VP70实现。在FPGA内部完成对于PPP帧的处理,此外,板级处理机还利用FPGA完成对各关键器件的初始化及相关配置。

PM5360通过一组SPI-3接口经接口适配模块进入FPGA内部。根据系统管理需求,线卡通过MPC860完成控制管理功能,基于VxWorks操作系统设计板级软件,完成初始化、各模块配置、运行状态监测、统计信息上报等功能。

3 PM5360应用要点与难点

由于PM5360集成的功能丰富,其内部电路复杂,可配置寄存器数量超过2 000个,因此其应用难度较大。根据笔者的调试经验,下面对该器件在通道化应用下的难点进行解释,主要包括间接寄存器读写方法及调度机的设计等。

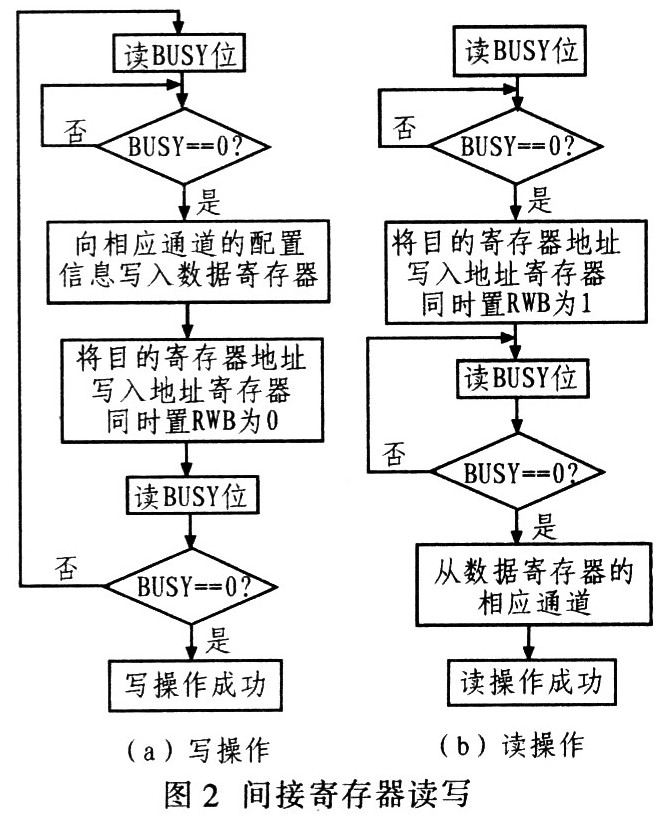

在PM5350的寄存器里,除了能够直接按照访存方式读写的寄存器外,还有大量间接寄存器,此类寄存器对POS模式下的器件工作方式尤为重要,但其配置方式特殊,因此本文对其使用要点进行总结,如图2所示。

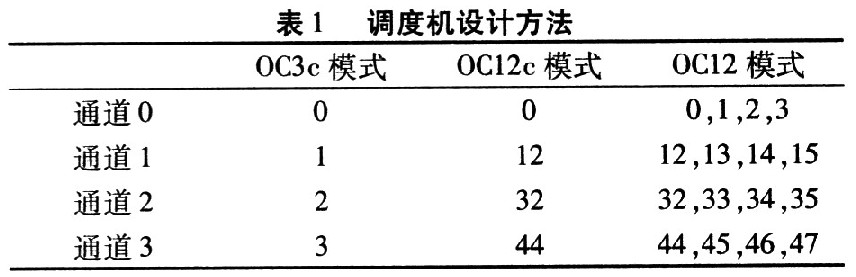

在PM5360内部有一个内置调度机,负责按照配置好的调度顺序读取各个通道的数据并放人接口缓存中,由于该芯片采用物理标识(PHID)和内部通道号同时存在的设计思路,而且通道化应用下单个物理通道内具有多个数据流,因此调度机的设计更复杂。

表1总结了调度机的设计要点,具体应用中,根据需要的模式将该表中的相应数值和对应的物理标识通过间接寄存器接口写入地址为0x0335的寄存器。

另外,在应用中需要注意的是,PM5360在每个通道内都置有2组并行的模块:xCFP和xTDP。其中xCFP包括RCFP(接收方向信元和帧处理器) 和TCFP(发送方向信元和帧处理器),xCFP用于0C12和OC48模式下的数据处理。xTDP包括RTDP(接收方向时间片数据通信处理器)和 TTDP(发送方向时间片数据通信处理器),用于OC3模式下的数据处理。在这两个模块的配置中,除了保证所有寄存器都按要求置位外,还需注意根据线路的实际特点完成各个通道以及内部子通道的加扰与解扰方式、使CRC校验算式等与实际线路一致,这一点在实际中常被忽略而成为伪故障,从而导致开发周期延长。

值得指出的是,由于PM5360内部结构复杂,模块众多,同时数据处理路径上的许多单元具有很强的关联性,因此厂家建议了一个较为严格的复位与配置顺序,基本原则可以总结为“按照数据流向,先完成逻辑单元配置,再完成物理单元配置,最后使能功能模块”,在实际中应照此原则执行。

4 支持动态模式的PM5360配置软件设计

本设计中的线卡支持多种工作模式,因此要求PM5360能够根据需要动态改变其内部寄存器配置,本部分给出其配置函数的设计要点。图3是支持动态模式的 PM5360配置函数。

该函数的基本形式为:PM5350_Config(unsigned charmode,unsigned char pathO_mode,unsigned char pathl_mode,unsigned char path2_mode,unsigned ehar path3_mode)。该函数的5个参数均为unsigned char类型,其中第1个参数mode用于指示器件处于通道化工作状态还是非通道化状态,其余4个函数分别代表其4个通道的工作状态。

根据路由器的体系结构特点,线卡等功能部件通过内部通信系统与主控联系,获取配置信息,并实时上报自身的运行状态信息和相关统计信息。因此,在图3中,函数PM5350_Config()中的参数是由主控下发的,函数接收到参数后按照该流程进行解释,从而完成配置。

5 性能测试

为了测试通道化单板的功能和性能,设计如图4所示的测试方案。其基本原理是:按照该线卡在实际网络中的应用特征,由测试控制台发出命令控制网络测试平台 AX4000按照所需模式发送数据至待测线卡,线卡接收数据后按照其内部处理机制完成报文处理,并最终经输出接口将数据送至测试仪,测试仪根据收到的报文情况给出丢包率等性能指标的测试结果。

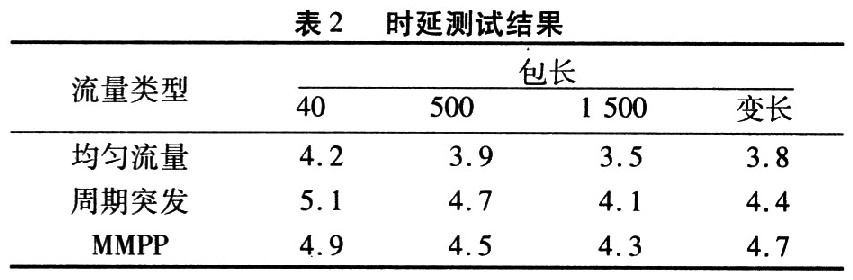

测试的主要内容是通道化混合信道类型支持能力,具体指标包括丢包率、时延和时延抖动等。测试结果表明,所设计的线卡能够支持需求分析所提出的全部功能指标,并且在100%链路利用率下,能够线速处理全部报文,丢包率为0,且各种性能指标符合设计要求。表2给出了时延测试结果,表明实际的时延指标满足设计要求。

6 结束语

本文基于PM5360和FPGA设计通道化OC48线卡,讨论设计需求,给出总体设计方案,重点分析PM5360的使用要点和难点,并给出能够动态变换工作模式的芯片配置方法。测试结果表明本文的设计能够满足实际需求。