0 引言

随着电子产品市场的不断扩大,闪存器无疑将获得极大的增长。这种增长在很大程度上取决于存储器的非易失性、低功耗、高密度和重量轻等特点。多项优点集于一身使得闪存器在移动电子和嵌入式领域中得到了极大的应用。而nand-Flash价格便宜量又足,性价比也很高,且十分轻便,抗震性也很不错,很适合用来做数码产品,现在的单片NandFlash芯片的存储容量已经可以做到4 GB。很难想像,在一个大小只有12×20×1.2mm的芯片里可以做到如此的容量。然而,由于Flash管脚多、体积小、一但使用后拆卸很不方便,因此,开发在线烧录系统也就成为嵌入式开发领域不可缺少的一步。

1 NandFlash简介

NOR和NAND是现在市场上两种主要的非易失闪存技术。Intel于1988年首先开发出NOR flash技术,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年,东芝公司发表了NAND flash结构,该结构强调降低每比特的成本和提供更高的性能,且可象磁盘一样通过接口轻松升级。NandFlash作为高数据存储密度的理想解决方案,可以达到高存储密度,并且写入和擦除的速度也很快。而其应用NAND的困难在于flash的管理问题和需要特殊的系统接口,Nand-Flash器件使用复杂的I/O口来串行存取数据,各个产品或厂商的方法可能各不相同。它用8个引脚来传送控制、地址和数据信息。NandFlash的读、写操作采用512字节的块,这有点像硬盘管理的此类操作。这样,基于NandFlash的存储器就很自然地可以取代硬盘或其他块设备,因为它也可以对称为块的存储器单元块进行擦写和再编程。任何flash器件的写入操作只能在空或已擦除的单元内进行,所以,在大多数情况下,在进行写入操作之前必须先执行擦除(在NandFlash闪存中每个块的最大擦写次数是一百万次)。总而言之,现在市面上常见的优盘、MP3和MP4等数码设备的存储系统都是采用NandFlash存储芯片来实现的。

2 在线烧录系统构架

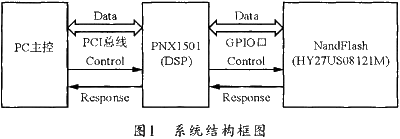

本文介绍的整个烧录系统由三部分组成,其中PC端通过PCI总线提供待烧录数据并负责控制PNX1051 DSP,而DSP则负责解析,以将上端PC传送的命令和数据通过控制GPIO管脚来控制NandFlash的通信时序以及烧录的实现。图1所示是该烧录系统的系统结构框图。

PNX1501是飞利浦公司推出的一款音视频处理芯片,该芯片的工作主频为300 MHz,并带有丰富的通信接口,可支持DDR、SDRAM、Nand-Flash、NorFlash和IDE等,此外,它还有30多个GPIO脚可以作为普通IO对外围芯片进行控制。本系统只用于实现对NandFlash裸片的烧写,因而不使用其自带NandFlash接口,而采用GPIO直接控制,这样在时序和逻辑上更加灵活。DSP与计算机之间的通信通过PCI总线实现,此外,DSP外扩有32MB DDR,该NandFlash用GPIO0~GPIO7作为数据口,GPIO8~GPIO12作为控制信号脚。对于市场上的专用烧录器件而言,其烧录速度的瓶颈在于数据传输。目前,大多数烧录器的数据传输速度都很低且自身缓存很小。烧录过程中需要与PC频繁进行数据通信,故在烧录比较大的文件系统时,需要花费很长的时间,而且操作极为复杂,更主要的是不能在线烧写,一但制成成品而需要更新时,就必须将Flash芯片拆卸下来,而对于本系统而言,PCI的传输带宽可以达到133 MB/s,即使是很大的文件系统,也能很快传输完毕,此外,由于是在线烧录,不需要对Flash进行拆卸,因此,对于产品的更新极为方便。本系统中选用的HY27US08121M NandFlash为三星公司生产的一款64MB Flash,该器件的块擦除时间为2ms,页写入时间为0.5 ms,可以实现高速读写。

3 系统软件

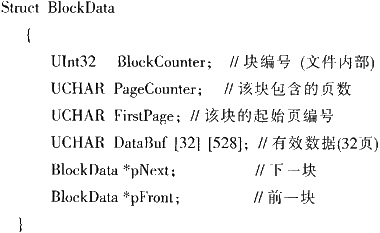

目前市场上Flash的存储空间均以块为单位进行管理,每一块大小为32页,每页包含512字节的有效数据空间和16字节的Spare空间,其中有效数据用来存放实际数据,Spare区间则用来存放有效数据的附加描述信息(ECC,坏块信息、索引编号等等)。不同的文件系统有各自不同的数据结构,其中最主要的两部分为ECC和坏块信息。坏块信息通常用该块的第0页或第1页的Spare区第6字节表示(0xFF为有效,其余为无效),ECC则是对全部有效数据进行一系列的异或校验后得出的校验值,通常为3字节(512字节校验)或6字节(256字节校验)。由于制造工艺的原因,Nand-Flash在生产过程中可能会产生坏块,而对于坏块而言,存储信息就可能会丢失,因而不能使用。每块Flash在出厂时已经把原始的坏块信息写入每块的第0页和第1页的Spare区,在擦除时一定要先检查是否为坏块,否则就会把坏块信息一并擦除(再也无法恢复)。此外,为了保证存储信息的可靠性,在从NandFlash中读取数据时还可以引入ECC校验,并对读取的每页512字节数据计算新的ECC,同时和该页Spare区存储的ECC进行比较,这样,可以纠正1 Bit位翻转,或检测2 Bit以上的翻转。 本系统中的烧录文件按照飞利浦的协议采用6字节的ECC,由于NandFlash以块和页来管理数据,因此,对于PC端,首先应将数据按照Nand-Flash结构进行映射,其代码如下:

之后便可将烧录文件数据填入DataBuf中,每填完512字节后计算ECC和其它Spare区间内容,填满32页就可开辟新的数据结构并挂入链表中。

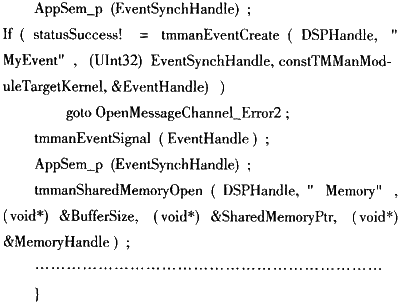

PC和DSP通信是该系统的关键。设计时可以采用消息方式,也可以在接收端DSP的外挂DDR中开辟一段共享区问,然后由PC直接将数据写入,再发送命令进行烧录。本系统采用第二种方式。对于飞利浦公司的DSP而言,该DSP在驱动中已经将其全部DDR空间映射到PC的物理空间了,因而可直接在驱动SDK中增加简单接口函数,以将有DSP开辟的共享区间的地址通过消息方式传送给PC,这样,PC就能直接对该区问进行读写了。该操作的具体代码如下:

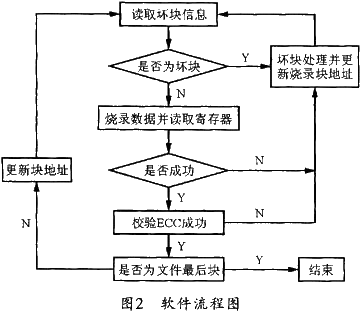

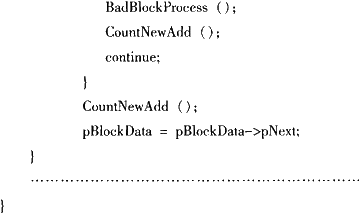

这样,当DSP接到PC发送的烧录命令时,系统便可读取共享缓冲区的内容并开始烧录Flash。其具体的流程如图2所示,部分函数源码如下:

设计时的具体时序可参照芯片资料所提供的时序电路来控制MMIO寄存器以实现GPIO的控制,在此不再赘述。需要注

意的是,NandFlash在烧录或擦除过程中,可能会失败并产生坏块。对于坏块的处理。不同系统有不同的方法,主要有直接Skip(跳过)和Reserved Block Area (使用保留块)等,本系统使用前一种方式。此外,为了可靠起见,在时间允许的情况下还应对烧录成功的块数据进行ECC校验,即读取全部数据来计算ECC并和烧录之前计算的ECC进行比较,以判断是否发生了位翻转,从而确定烧录是否正确。如果发生两位以上的翻转,则说明该块烧录错误,应重新选择新块烧录并将原块标记为坏块。

4 结束语

对DSP外部Flash编程虽然不是一项关键技术,但是它在整个DSP嵌入式系统开发过程之中却起着至关重要的作用,如何方便、快速地实现对引导文件(BootLodaer)和文件系统的烧录,更是直接影响产品的生产与更新的重要环节。通过本系统可以迅速快捷地实现前期所有启动文件的烧录,实际测试证明:烧录40 MB的文件系统只需要不到3分钟,这一点无论从速度上,还是经济上都优于通用编程器件。