一种HDLC数据转发的全自动硬件引擎设计

2008-10-14

作者:文冠果 陈家锦 何刚跃 赵

摘 要: 讨论了一种HDLC协议数据转发的全自动硬件设计。在SDH产品的ECC接口中采用硬件实现" title="硬件实现">硬件实现,通过自动控制BD的方式,实现HDLC协议的数据重新打包转发、错误处理、重发帧数据等操作,不必CPU干预。该设计实现了两个ECC口收发全双工、8个DCC口点对点同时收发的高速率、多通道" title="多通道">多通道设计。

关键词: ECC HDLC BD

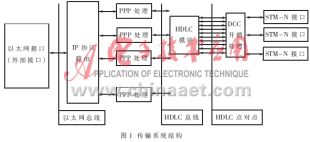

在传输产品中,IP over SDH的基本思路,是将IP数据通过点到点协议(PPP)直接映射到SDH帧,从而省掉了中间复杂的ATM层。具体作法是先把IP数据报封装进PPP分组,然后再利用高级数据链路" title="链路">链路控制规程HDLC按照RFC1662的规定组帧,最后将字节同步映射进SDH包中,加上相应的SDH开销置入STM-N帧中。IP over SDH简单的系统结构如图1所示,其中PPP层的功能包括IP多协议封装、差错检验和链路初始化控制,而HDLC为PPP封装的IP数据包提供定界,并用01111110表示一帧的开始和结束。

本文讨论如何用全自动硬件方式实现图1中所示的HDLC模块。

1 传统的CPU实现方式

在图1中,HDLC模块实现一个HDLC总线到多个点对点HDLC接口之间的数据转发。将HDLC总线的接口称为ECC口,HDLC点对点接口称为DCC口。传统的实现方法如图2所示,是若干HDLC控制器芯片加一块CPU实现ECC到DCC的数据转发功能。CPU通过软件配置,向HDLC帧中插入或提取用户自定义的10个字节(包括源地址、目标地址、DCC端口号、帧长度等)。以下行为例,HDLC控制器在ECC接口接收数据后,向CPU申请使用SRAM中的缓冲区,CPU进行仲裁,分配缓冲区描述符BD,数据就可以存放在SRAM中。CPU在这些数据发送时需要指定DCC通道。由于数据量较大,每一帧都要进行BD的处理,且数据申请导致中断处理频繁,软件很容易出错。

另外,随着单板集成度的提高,ECC接口的数据量越来越大,DCC接口的通道也越来越多。如果采用传统的CPU实现方式,就必须不断增加HDLC控制器,所要求的CPU性能也越来越高,这在技术上难以实现,成本上也不能接受,因而必须确定一种更经济、有效的技术方式来实现大容量、高效率、低成本的ECC转发技术。采用硬件方式,无须或尽量减少CPU的干预,在ECC接口实现自动的HDLC数据转发。

笔者的目的是将HDLC控制器和CPU的大部分功能用硬件实现,在整个运作过程中,不需要CPU实时协助,可实现全自动控制,CPU只需在开始进行一些初始化和配置工作,同时为CPU提供一些统计信息,方便CPU了解模块数据传送的性能。

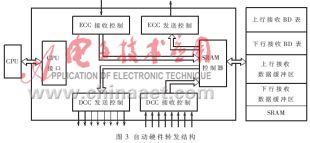

2 全自动硬件结构设计

硬件结构如图3所示,可划分为六大块:ECC接口的发送模块" title="发送模块">发送模块、ECC接口的接收模块" title="接收模块">接收模块、DCC接口的发送模块、DCC接口的接收模块、SRAM控制器和CPU接口。

ECC_TX控制:

·仲裁DCC_RX发过来的数据申请;

·从SRAM内读取数据到内部;

·按照要求添加前10个字节的信息;

·按照协议产生新的16位CRC;

·按照协议发送数据;

·按照协议进行重发操作;

·在操作正确完成后,更新BD和发送指针。

ECC_RX控制:

·实时监控HDLC总线上的变化;

·解析正确的HDLC数据包,进行CRC检查;

·接收属于本地址的数据包到SRAM内;

·在发生错误的情况下,放弃已经存入SRAM内的数据;

·在数据包正确接收到SRAM之后,产生新BD并更新接收指针。

DCC_RX控制:

·接收的逻辑有8组,可同时接收;

·实时监控HDLC点对点的数据变化;

·解析正确的HDLC数据包,进行CRC检查;

·接收数据包到SRAM内;

·在发生错误的情况下,放弃已经存入SRAM内的数据;

·在数据包正确接收到SRAM之后,产生新BD并更新接收指针。

DCC_TX控制:

·发送是由自己控制,只需一套逻辑,8个通道轮流发送;

·判断是否有新的数据要发送(判断发送指针是否与接收指针一致);

·从SRAM内读取数据到内部;

·分析前10个字节的信息,决定8个发送端口的其中1个发送;

·去除前10个字节的信息;

·按照协议产生新的16位CRC;

·按照协议发送数据;

·在操作正确完成之后,更新BD和发送指针。

SRAM控制器:

·这一部分实现数据的存取,ECC接收和发送各1个,DCC接收8个,DCC发送1个,共有11个数据申请;

·考虑到数据流量,SRAM采用16位宽。

CPU接口:

·配置前10个字节的信息,设置源地址和目标地址;

·复位通道;

·提供统计信息,供CPU分析运作情况。

3 数据流

(1)上行数据流

如图4所示,DCC接收到的数据(8个同时)→正确数据存放于SRAM内→数据取出,添加10字节,从ECC_TX发送出去。

(2)下行数据流

如图5所示,HDLC总线的数据→地址匹配且正确的数据存到SRAM内→数据取出,从DCC_TX的其中一个端口发送出去。

4 CPU干预程度分析和性能分析

(1) 系统使能后硬件即可正常工作,不需要CPU任何配置,相当于一个自动的微引擎;

(2) 发送部分不受寄存器控制,始终在运作,通过与接收的BD指针比较决定有没有数据要发送;同理,接收部分通过BD指针的比较决定SRAM中还有没有BD空间存放数据,通过BUF指针比较决定要不要存放数据;

(3) 接收部分和发送部分有一个共同的BD和BUF基准地址,有一个各自初始值为0的指针,接收部分每接收一帧数据,指针加2,发送部分可以看到这个指针的变化;

(4) 通过BD的结构,可以完成接收与发送部分关于数据帧的长度通知;接收部分收到一帧,将统计下来的帧长度存放在BD中,发送部分读到BD中的帧长度,按该长度向SRAM申请数据;

(5) 通过wrap设置,可以完成自动检测空间和返回缓冲区起始地址,重用缓冲区;

(6) 错误处理可以自动恢复和重发,只有发生致命错误,如下溢时,才需要CPU对系统进行复位;

(7) 如果考虑最差情况下的速率,最高速度是5MHz(ECC_HDLC接口),现在SRAM采用16位操作,并且FIFO只有一级,则访问频率为5MHz/16,一次SRAM访问需要5个时钟,此时最坏情况是其它9个接口也同时申请数据操作(共11个接口,ECC_HDLC占两个接口,但在5MHz情况下这两个接口只能有一个在运作之中)。此时系统时钟必须满足以下条件才不会产生下溢错误: 5MHz/16<sys_clk/(9×5+5),其中(9×5+5)为9个其它设备的数据申请以及它自身数据操作需要的时间。此时得到的系统最小时钟为:15.625MHz。这个速率对FPGA的硬件实现来说,是毫无困难的。

本系统实现SDH产品中ECC接口到开销处的数据交换,以HDLC协议实现ECC和DCC两边的数据传送,整个传送过程不需要CPU实时控制。采用该设计,可不再使用多个HDLC控制器,CPU可由原来的高性能改为低档CPU,极大地降低成本,同时可具有良好的扩展性。该设计采用Xilinx的Spartan 600E实现,已成功在产品中应用。

参考文献

1 ISO/IEC 3309,1993,Information technology—Telecommuni-cations and information exchange bet-ween systems—Highlevel data link con-trol(HDLC) procedures—Frame structure

2 文冠果. 一种可重用的SoC通讯微引擎结构设计.微电子学与计算机,2004;21(1)

3 文冠果. 一种新型的128路多通道HDLC引擎设计.微电子学与计算机,2004;21(9)