摘 要: 提出了一种基于FPGA动态局部重构技术的无线传感器网络节点设计方案,通过FPGA高效的计算能力来提高节点的处理能力,同时采用动态局部重构技术进行功耗控制。根据所提方案进行了硬件平台的设计,并在此平台上对可重构的流程及实现方法进行了验证。实验结果表明,该方案能够实现无线传感器网络节点的部分可重构,在减小功耗的同时具有较强的运算能力。

关键词: 无线传感器网络;现场可编程门阵列;动态局部重构

无线传感器网络WSN(Wireless Sensor Network)是一种将传感技术与网络通信技术结合起来的新兴技术,可以使人们方便快捷地监测、采集、获取信息,能够满足军事、环境监测、环保、 医疗、农业等多领域的应用需求。

无线传感器网络通过飞行器播撒、人工放置等方式将网络节点任意布置在监测的区域中。典型的无线传感器网络由传感器节点、汇聚节点、管理节点构成,这些节点通过自组织方式进行组网。典型传感器节点主要由传感器单元、数据处理单元、通信单元和电源单元组成[1-2],如图1所示。

通常情况下,无线传感器网络主要应用于数据速率较低、对数据处理需求不高的场景。因此,对于此类应用,基于微处理器的传统无线传感器节点即可满足对计算和处理性能的需求。另一方面,不同的应用场景对更强劲处理能力的节点要求越来越强烈[3]。例如,音频视频数据以及数据的加密处理等都需要提高节点的处理能力。

使用高性能的处理器可以显著提升无线传感器网络节点的处理能力。FPGA拥有媲美专用集成电路ASIC的运算性能,同时,由于FPGA具有灵活的特点,使得FPGA应用于多个领域取得了很好的效果。另外,基于FPGA的动态局部重构技术也为FPGA更加灵活同时更好地控制芯片能耗提供了一种方法。基于以上特点,可重构FPGA可以作为处理器来构建新型无线传感器网络节点。

1 FPGA动态局部重构技术及实现方法

FPGA是在可编程器件的基础上发展起来的。目前,商用FPGA一般是基于SRAM技术的查找表结构,通过对FPGA芯片内部SRAM编程配置查找表,实现具体的功能。

FPGA开发的一般流程为:设计、综合、布局布线生成比特流文件,然后下载FPGA执行。当需要实现不同功能时,重新进行上述流程并下载生成的新的比特流文件即可。FPGA的动态局部重构是指对FPGA的部分区域进行实时重配置,在此过程中其余部分不受影响。动态局部可重构技术对提高系统集成度、增强系统灵活性、提升容错能力,同时降低系统成本和功耗具有重要的实际意义。

FPGA动态局部重构有多种实现方法,例如JBits[4]、基于模块化设计[5]、基于差别化设计的实现方法[6]、EAPR(Early Access Partial Reconfiguration)[7]等。其中, EAPR是比较常见的方法。在设计时将整个设计根据不同的功能划分成不同的模块,包括静态模块和可重构模块;同时在FPGA内部划分出静态区域和可重构区域。在系统运行中保持静态区域加载静态模块不变,可重构区域加载可重构模块完成系统功能。

2 设计方案

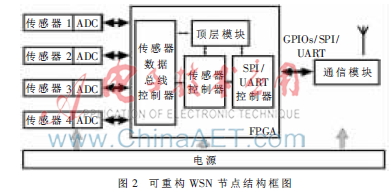

根据无线传感器网络节点的结构及动态局部重构技术的需要,设计了基于FPGA动态局部重构无线传感器网络节点,功能框图如图2所示,其中心部分是一个可以提供动态可重构功能的FPGA,围绕着这个核心器件部署传感器模块、 通信模块和电源模块。

2.1 传感器模块

传感器模块是无线传感器网络节点中最主要的功能部分,它将感知对象的信息通过处理转化成处理器可以识别的信息形式。本设计中的传感器模块提供多个不同类型的传感器接口,通过ADC转换后与处理模块相连。传感器的控制主要通过FPGA内部建立相应的控制器实现。

2.2 数据处理模块

数据处理单元是无线传感器网络节点的核心部分,主要提供三方面的功能。

(1)传感器控制和数据处理

FPGA内部逻辑的可编程特性使其可以方便地通过硬件描述语言(HDL)实现对传感器的控制。为了保证传感器节点的可扩展性,同时使各传感器更易于接入部分动态可重构控制模块,将传感器控制器封装成具有相同数据输出格式的模块。在传感器控制器后端,可根据需要构建数据处理模块。传感器数据总线控制器通过数据线与数据处理模块相连。

(2)部分动态可重构控制

部分可重构功能是处理模块的主要特点。根据FPGA动态局部重构的实现方法,需要在FPGA芯片内部划分出静态区域和可重构区域。依据EAPR设计流程完成动态局部重构设计,在可重构区域内通过控制加载不同的功能模块实现部分可重构功能。

(3)数据收发控制

数据收发控制主要完成与数据收发模块的接口功能。通过在FPGA内部建立控制逻辑完成,将处理模块处理好的数据发送至通信模块,同时接收从通信模块返回的数据。

2.3 通信模块

通信模块通常由无线收发模块组成,完成节点之间的通信。基于蓝牙、ZigBee等技术射频集成芯片一般可以满足数据收发模块的功能需求。

2.4 电源模块

电源模块是传感器节点的能量供应部分,完成对整个节点的电源支持。根据应用场景和需求,一般可通过各类电池或固定电源供应模块来满足要求。

3 FPGA动态局部可重构无线传感器节点实现

3.1 硬件实现

根据图2所示的功能框图,选择了气温传感器和气压传感器,以Xilinx的Virtex-5系列FPGA作为处理模块,数据收发模块采用CC2530完成。节点实物图如图3所示。

3.2 动态局部可重构功能的实现

根据EAPR设计流程,节点的可重构功能实现主要分为以下几个步骤。

(1)设计的划分和实现

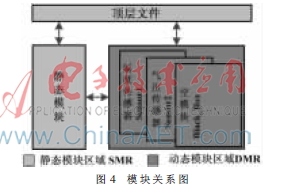

通过分析整个设计的功能,将其分为静态模块设计和可重构态模块设计两部分,各模块的关系框图如图4所示。

顶层模块主要进行可重构模块和静态模块之间的划分,并定义各个模块之间的连接关系、整个设计与外部的接口和信号。可重构模块PRM(Partial Reconfigurable Module)是在重构过程中进行动态加载的模块。本设计所选取的传感器皆为数字传感器,因此设计PRM时,需通过HDL完成传感器控制功能,然后根据顶层模块的定义将传感器控制器进行封装。

静态模块SM(Static Module)是在重构过程中保持不变的部分。本设计中的静态模块主要功能是完成传感器控制器读出的传感器数据的数据处理。静态模块只保留与顶层模块和可重构模块的接口,没有对外的IO端口。本设计的静态模块主要完成数据收发模块功能,即完成与通信模块连接的UART接口。

(2)综合

完成上述设计之后,利用综合工具将完成的HDL程序进行综合,产生网表文件。

(3)放置

主要是将综合生产的网表文件按照设计分配至区域中。在添加约束后将各模块分配至图5所示的u1、u2区域。其中,u1对应的是静态模块区域SMR(Static Module Region),u2对应的是可重构模块区域PMR(Partial Module Region)。

(4)合成

将设计的各个部分组合起来形成完整的设计。

3.3 通信模块实现

通信模块采用TI的CC2530芯片,是应用于2.4 GHz的SoC解决方案,它集成了ZigBee协议栈,可作为WSN的解决方案。将CC2530作为通信模块的核心器件,接收从FPGA内部数据后直接发送出去。

3.4 实验结果

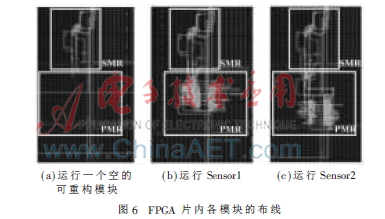

各模块图布线后版图如图6所示。其中,图6(a)表示运行一个空的可重构模块时FPGA内部布线情况;图6(b)表示运行Sensor1时FPGA内部布线情况;图6(c)表示运行Sensor2时FPGA内部布线情况。从图中可以看出,当只加载顶层模块时,设计只占FPGA很小一块面积;而Sensor1和Sensor2运行时,顶层模块是相同的,只有可重构模块发生改变。使用的逻辑资源越少,功耗越低,因此可通过加载不同模块实现休眠、Sensor1功能、Sensor2功能,尽可能地减少资源占用,降低功耗。

可重构配置文件与全局配置文件大小的比较如表1所示。从表中可以看出,部分可重构方式的配置文件要比全局重构配置文件小得多,表明部分可重构配置的速度更快。

本文提出了一种新的无线传感器网络节点结构设计方案,通过基于FPGA动态局部重构技术,利用FPGA的高效计算性能,提高了无线传感器网络节点的处理性能。

参考文献

[1] 孙亭,杨永田,李立宏.无线传感器网络技术发展现状[J].电子技术应用,2006,32(6):1-5.

[2] 孙利民.无线传感器网络[M].北京:清华大学出版社,2005.

[3] DE LA PIEDRA A,BRAEKEN A,TOUHAFI A.Sensor systems based on FPGAs and their applications:a survey[J].Sensors,2012,12(9):12235-12264.

[4] GUCCIONE S A,LEVI D.Jbits:a java-based interface to fpga hardware[J].Xilinx Inc,San Jose,CA,1998.

[5] Xilinx Corp.Difference-Based Partial Reconfiguration.2012.[2014-01-25].http://www.xilinx.com.

[6] Xilinx Corp.Partial Reconfiguration of Xilinx FPGAs Using ISE Design Suite.2012[2014-01-25].http://www.xilinx.com.

[7] Xilinx Corp.Early Access Partial Reconfiguration User Guide.2012.[2014-01-25]http://www.xilinx.com.