摘 要: 根据实际项目需求设计了一种实时阵列信号处理系统,采用多路高速光纤作为数据输入、输出接口;4片处理器组成互联的拓扑结构,任何两片处理器之间都可以互相传送数据,多片处理器可同时对数据进行高速处理;系统配备了大容量存储器,可满足大量数据的存储要求;采用两片现场可编程门阵列器件对系统接口、时序进行控制;为每片处理器分配了处理任务,并对信号处理算法运行时间及数据传输时间进行评估。该系统已在实际项目中运行,充分满足项目要求,运行稳定,验证了本系统设计的可行性。

关键词: 实时系统设计;阵列信号处理;算法运行时间评估;处理器

0引言

在现代雷达、测向等系统中需要对阵列信号进行实时处理。阵列信号通道数多,数据量大,信号处理实时性要求高[1-2]。目前,FPGA和DSP成为这类系统中信号处理的主要器件。参考文献[3]~[5]均采用FPGA来实现数字信号处理算法。FPGA对方法简单和规则的运算来说效率很高,所设计系统具有集成度高、体积小和快速实时处理等优点,但其灵活性差、开发成本高、系统升级困难,特别是在浮点运算处理时开销呈几何级增长。DSP技术具有灵活性强、开发周期短以及系统升级维护方便等特点[1,6],比较适合算法复杂的数字信号处理。采用FPGA加DSP的方法进行系统设计,兼顾二者的优点[7],更适合雷达、测向等大型系统,使系统设计更加灵活,降低了开发难度和成本,易于系统升级与维护。参考文献[1]、[6]、[8]、[9]均采用了这种方式进行系统设计。

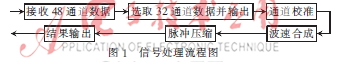

在某实际项目中,要求设计一套实时阵列信号处理系统,阵列信号通道数为48,每通道数据长度为2 400,根据高、低频段选取不同的32通道数据进行处理,最小处理周期为50 ms,并将选取的32通道数据和处理结果输出。信号处理流程如图1所示。

针对项目要求设计了一套吞吐速率高、处理速度快、存储容量大的实时阵列信号处理系统,并在实际工程中进行了应用。系统采用FPGA加DSP的设计方式,DSP用于对数据的实时处理,FPGA用于对时序和接口的控制。

1 系统设计

1.1 处理器设计

TS201是一款高性能数字信号处理器,具有运算速度快、接口丰富、扩展能力强等特点,特别适合雷达等处理数据量大、实时性要求高的信号处理系统[10]。

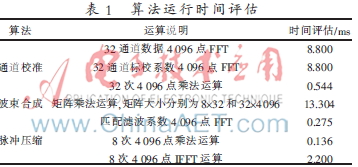

根据TS201处理器的处理速度,对系统中所用到的通道校准、波束合成和脉冲压缩信号处理算法运行时间进行评估,如表1所示。

表1中所有时间合计为34.059 ms。综合考虑,本系统需要4片TS201处理器,1片用于接收48通道基带数据,1片用于脉压运算及处理结果输出,另外两片处理器主要用于通道校准、波束合成运算及32通道基带数据输出。

1.2 控制设计

选用两片FPGA(型号为XC5VLX50T)用于系统接口和时序控制。

XC5VLX50T是赛灵思公司Virtex-5系列中的一款产品。该型号FPGA具有480个用户I/O,可以被配置成各种电平标准;最大可提供2 160 kbit块式RAM和480 kbit分布式RAM;单片集成12个Rocket IO模块,完全满足本系统的设计要求。

1.3 接口设计

主要接口包括数据的输入和输出,根据项目要求均采用光纤进行传输。48通道基带数据分别来自3个不同的数字接收机柜(分别用A、B、C表示),传送数据的通道数分别为8、24和16,需要3个接收光口。基带数据转发光口要求至少为3个,以便提供多台设备使用。处理结果输出光口要求大于2个。这里为每个处理器配备3个光纤收、发接口。

光口收发器采用Rocket IO模块。Rocket IO是一种高速串行收发器,采用两对差分信号进行数据的发送和接收,8 B/10 B编码可以避免数据流中出现连0或者连1串,通信速率可达800 Mb/s~3.125 Gb/s。考虑到稳定性问题,本系统中光口的速率设计为2.5 Gb/s。由于采用了8 B/10 B编码,因此实际有效数据传输速率为2.0 Gb/s。

发送数据时,处理器将数据通过外部接口写入到FPGA的FIFO中,然后数据再由FIFO通过Rocket IO模块发送出去。接收数据时,数据首先进入Rocket IO模块,经过转换之后写入到FPGA的接收FIFO中,处理器通过外部总线从接收FIFO中读取数据到内存进行处理。

1.4 系统设计

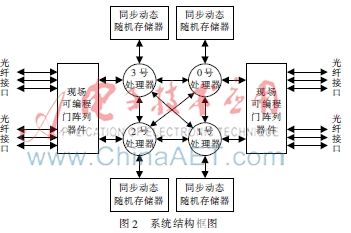

系统结构如图2所示。

每个处理器都通过Link口分别与其他3个处理器互联,数据可以在任何两个处理器之间进行传输。剩余的一个Link口被引出,可通过外接线缆的方式与其他系统TS201处理器的Link口相连,便于系统升级及其他项目应用。

由于阵列信号数据量较大,处理器内存很难满足存储要求。为此,在本系统中每片处理器都搭载了总容量为512 MB的SDRAM。

系统时钟频率为50 MHz,处理器内核时钟频率为600 MHz。处理器通过外部总线访问SDRAM及光口FIFO的速率为400 MB/s。

2 系统分析

2.1 任务分配

与0号处理器连接的3个光口分别与3台数字接收机柜相连,用于接收48通道基带数据,并按照项目要求分高、低频段选出不同的32通道数据,通过两个Link口分别传送到2号和3号处理器。

2号处理器收到32通道数据后,将该数据通过3个光纤接口输出;然后开始对前16通道数据进行信号处理,包括通道校准和子阵波束合成;最后将波束合成结果通过Link口发送到1号处理器。

3号处理器完成的任务与2号处理器相同,只是处理的数据为后16通道。

1号处理器完成对2号和3号处理器波束数据的接收,并进行全阵波束合成和脉冲压缩处理,最后将处理结果通过该处理器的3个光纤接口输出。

2.2 系统评估

为实现传输的稳定性及处理器接收速率与光纤传输速率的最佳匹配,控制每个接收机柜发送数据的速率为160 MB/s,并采用图3所示的时序进行发送,能充分利用系统传输带宽。

从图3可以看出,同一时刻最多只有两个光纤在传输数据。数字接收机柜A的8通道数据发送完成后空闲1 ms,然后数字接收机柜C开始发送数据。0号处理器接收完3个机柜发送的48通道数据所用时间相当于机柜A的发送时间、机柜C的发送时间及空闲时间的和,约为3.88 ms。32通道数据以DMA的方式同时向2号和3号处理器传送数据,需要时间为1.536 ms。因此,0号处理器完成数据的接收和发送共需要花费时间约5.416 ms。

2号处理器首先接收32通道基带数据,并通过光纤接口发送,然后对前16通道数据进行通道校准和波束合成,最后将处理结果通过Link口发送到1号处理器,其运算时间评估如表2所示。32通道基带数据要同时通过3个光口发送,因此处理器访问一个光口的平均速率变为133 MB/s。

2号处理器总的运行时间为22.535 ms。TS201处理器内存由6个存储块组成,4条内部总线分别与6个内存块相连,当参与运算的数据分别位于不同的内存块时可提高运算效率。

3号处理器算法运行时间评估与2号处理器相同。

1号处理器通过Link口分别接收来自2号和3号处理器的处理结果,并将二者再次进行波束合成,然后进行脉冲压缩,最终输出脉冲压缩结果。1号处理器运行时间评估如表3所示。

1号处理器总的运行时间为4.168 ms。根据项目要求输出数据点数缩短为每波束1 760点,同时由3个光纤口输出。

通过以上分析可知,所设计系统在功能和实时性上均能满足项目要求。

3 应用

本文所设计系统已被成功应用于某大型项目中。在该项目中,本系统实时接收来自3个接收机柜的48通道基带数据,并分高、低频段选取不同的32通道数据,先通过光纤接口输出,然后完成对32通道数据的校准、波束合成及脉冲压缩处理,最后通过光纤接口将处理结果输出。该系统实现了项目所要求的各种功能和性能指标,并且系统运行稳定,达到了预期目标。

4 结论

根据项目要求,本文提出了一种基于DSP和FPGA的实时阵列信号处理系统设计方法。系统通过高速光纤接口实现外部数据的接收和发送,内部处理器之间通过Link口进行数据交换;处理器每秒48亿次40位浮点乘累加运算及多处理器设计使系统具备超强的实时运算能力;单片处理器24 MB内存及扩展的256 MB外部存储器,充分满足大数据量的存储需求。该系统已成功应用到某大型项目中,实现了项目提出的各种功能及指标要求,验证了本系统设计的可行性。

本系统在接口、存储资源、处理速度等都方面都有冗余,易于系统升级改造以及满足其他项目的应用需求;系统结构采用对称设计,对不同结构的算法具有较强的适应能力;本系统也是一种通用的实时信号处理运算平台,可直接应用于其他项目的实时信号处理系统,对同类实时信号处理系统的设计具有重要的参考价值。

参考文献

[1] 王魁,杨健.基于TS201的外辐射源雷达信号处理系统[J].数据采集与处理,2013,28(4):444-449.

[2] 王峰,李婧,刘俊,等.宽带数字阵雷达数字波束形成系统研究[J].雷达学报,2013,2(3):314-318.

[3] GUPTA P, GUPTA D. Design and implementation of FPGA based signal processing card[J]. International Journal of VLSI design & Communication Systems(VLSICS), 2011,2(3):131-137.

[4] MURALI H S, MEENAKSHI M. Design and development of FPGA based data acquisition system for process automation[J]. Communications in Control Science and Engineering(CCSE), 2013,1(1):7-11.

[5] Zhang Xiaojing, Yue Yajie, Sha Chenming. Design and implementation of a multichannel pulse compression system based on FPGA[J]. Journal of Computers, 2013,8(1):121-128.

[6] 竺红伟,梁之勇.一种通用无人机载SAR实时信号处理系统设计[J].航天电子对抗,2013,29(3):29-31.

[7] Wu Wei, Wang Jun, Li Wei, et al. Design methods of multi-DSP parallel processing system[C]. World Congress on Computer Science and Information Engineering, 2009,3: 458-464.

[8] 周杰,李小娟,张伟,等.一种通用雷达信号处理系统设计[J].电子科技,2013,26(5):91-94.

[9] 李鑫,姜明.多核DSP高速实时信号处理系统设计[J].光学技术,2012,38(1):116-120.

[10] 陈新峰,张军杰,赵非,等.基于TS201芯片的雷达信号处理机设计[J].电子设计工程,2011,19(13):156-158.