EUV是7nm节点之后的必然趋势

2019-08-20

过去几十年,半导体产业在摩尔定律的指导下获得了高速的发展,为了满足摩尔定律“同等面积芯片集成的晶体管数每18个月翻一番”的要求,晶圆厂一直在推动工艺制程的更新。但随着节点的演进,产业界普遍认为传统的光刻将会在65nm或者45nm的时候遭受到障碍,为此他们寻找新的解决办法,EUV就是他们的主要选择。

所谓EUV,是指波长为13.5nm的光。相比于现在主流光刻机用的193nm光源,新的EUV光源能给硅片刻下更小的沟道,从而能实现在芯片上集成更多的晶体管,进而提高芯片性能,继续延续摩尔定律。

芯片行业从20世纪90年代开始就考虑使用13.5nm的EUV光刻(紫外线波长范围是10~400nm)用以取代现在的193nm。EUV本身也有局限,比如容易被空气和镜片材料吸收、生成高强度的EUV也很困难。业内共识是,EUV商用的话光源功率至少250瓦,Intel还曾说,他们需要的是至少1000瓦。除了光刻机本身的不足之外,对于EUV光刻机系统来说,光罩、薄膜等问题也有待解决。

近两年内来看(2019-2020 年),7nm 节点后光刻技术从 DUV 转至 EUV,设备价值剧增。当前使用的沉浸式光刻技术波长 193nm(DUV,深紫外光),而当进行 7nm 以下节点制造时就需采用波长 13nm 的 EUV 光刻机。根据 ASML 公布的路线图,EUV 光刻机首先于2018年在7nm及以下逻辑芯片开始应用。在EUV设备制造过程中,由于EUV波长仅13nm,没有合适介质进行精准折射,因而所有光路设计均采用反射的形式,设计更加复杂,对精度要求极高,制造难度极大。全球只有 ASML 生产的 NXE3400B 是唯一支持 7nm 及 5nm 的EUV 光刻机,单台机器价值约 1.17 亿美元。

台积电拥有 EUV 设备最多,为 ASML 最大客户,三星次之。EUV 设备作为 7nm 以下制程必备工艺设备,对厂商最新制程量产具有至关重要的作用。由于对精度要求极高,台积电与 ASML 在研发上有相关技术配合。台积电与三星是 ASML 前两大订购客户。对于中国大陆厂商来说,并不存在“瓦森纳协议”限制向中国出口最先进 EUV 光刻机的情况。中芯国际目前已从 ASML 预定 1 台 EUV 光刻机,这对于中芯国际未来发展 7nm 以下技术具有积极意义。英特尔 7nm 采用 EUV 双重曝光技术已有提前布局,仍有望按原定计划量产。

在今年的5月份,三星就发布了基于7nm EUV工艺的下一代手机处理器Exynos 9825。三星称,通过7nm EUV工艺,新处理器的生产过程可以减少 20% 的光罩流程,使整个制造过程更简单,还能节省时间和金钱,另外还达成40%面积缩小、以及20%性能增加与55%的功耗降低目标。台积电也在6月份宣布批量生产7nmN7+工艺,这是台积电第一次、也是行业第一次量产EUV极紫外光刻技术。并表明这种新工艺的产量已经可以达到原来7nm工艺的水平了。

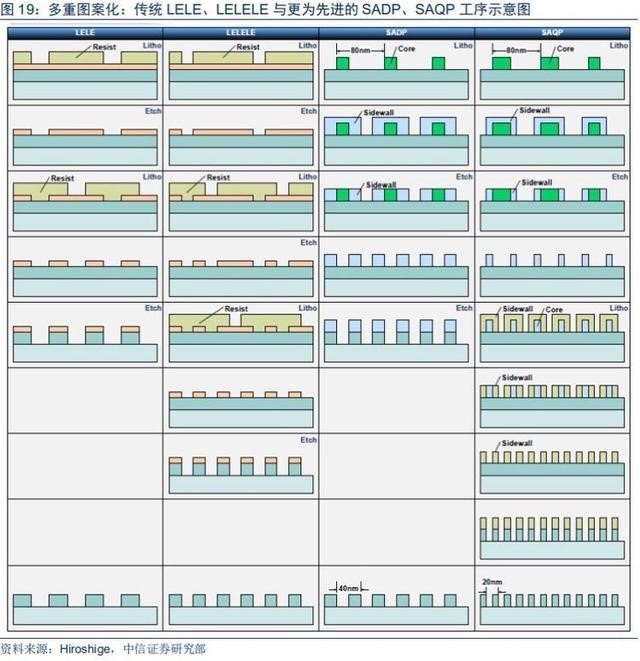

在EUV之外,7nm 节点还有另外一种技术路径,即采用 193nm 波长+SAQP 四重图案化达到所需分辨率。下图黄线中红点处即代表采用193i 浸没式光刻机+SAQP四重图案技术,对应英特尔所选择的技术路线;7nm在蓝线中蓝色区域代表采用EUV光刻机单次图案化,代表台积电和三星所选择的技术路线。在之后的 5nm 节点,193i 光刻机技术难度更大,采用 EUV 双重图案化是较为合理的选择。

从成本角度考量,193i 多重图案化在某些场景仍然是最为经济的选择。根据东京电子测算的不同曝光工艺标准化晶圆成本,EUV 单次曝光的成本是193i(DUV)单次曝光的 4倍,而 193i 四重图案曝光 SAQP 是 3 倍,EUV 单次曝光技术的晶圆成本高于自对准四图案曝光(193i SAQP)。采用 193i SAQP 仍然具有成本优势。

尽管 193i更为经济,但EUV 仍是未来更先进制程不可或缺的工具。英特尔在 Fab42 工厂已有布局 EUV,计划用于 7nm 及以下节点,由于英特尔 7nm 节点不再面临 SAQP 四重曝光技术难题,而是EUV 双重曝光,有望重回正轨按原定计划 2020 年量产。