软件友好型的硬件提供了最大的灵活性,敲开了高性能数据加速的大门

2020-03-23

来源:电子信息产业网

在云计算和边缘计算中,业界渴求能够支持各种应用的高性能。为了满足这一需求。

亚马逊(Amazon)、Facebook和微软(Microsoft)等超大规模用户采用的第一批加速器都是大幅度定制的设计。这些公司能够在打造自己的板卡设计中确保所需的规模经济,无论是基于自己设计的专用集成电路(ASIC),还是采用现成的FPGA和GPU。从成本和时间的角度来看,对于企业数据中心和边缘计算用户来说,他们难以在这种定制芯片级设计中找到合理的规模。然而,设计定制的ASIC和板卡并不是必需的。对诸如以太网和PCIe等标准接口的需求,不仅使使用标准板卡级产品成为可能,而且也是可取的。

作为一家长期提供硬件加速产品的供应商,BittWare一直在为从高性能计算到云加速到仪器仪表等众多领域内的客户设计采用PCIe尺寸的、基于FPGA的板卡,并在这方面积累了丰富的经验。现在,作为Molex集团的子公司,BittWare能够充分借助其全球供应网络以及与戴尔(Dell)和惠普企业(HP Enterprise)等服务器供应商的深厚关系。BittWare是唯一一家可与多家主流FPGA供应商合作的重要批量化供应商,能够满足企业客户的质量认证、验证、产品生命周期管理和支持需求,这些客户希望为关键任务型应用去大规模部署FPGA加速器。

在这些应用中,BittWare实现的一个重要差异化在于该公司为其基于FPGA的加速器提供了广泛的软件支持。每个加速卡均配有适用于Linux和Windows系统的驱动软件,可通过PCIe和以太网连接将其快速集成到各种系统中。除了支持主CPU和加速卡之间的通信外,该驱动还支持接入加速卡上的嵌入式固件。这个固件可以处理众多管理和自检功能。

它们使FPGA电路能够根据需要的新功能重新进行配置,此外还提供了一些对功耗、电压和温度的监测程序。如果主机系统中的冷却功能失效,那么担任管理者的固件可以关闭加速卡,以避免热过载。此外,软件组合包还包括各种参考设计,以便开发人员能够快速构建配置,使他们可以测试加速卡的功能并开始在其自己的应用上工作。

对于最新一代的加速卡,BittWare与Achronix紧密合作。Achronix是唯一一家能够同时提供独立FPGA芯片和嵌入式FPGA(eFPGA)半导体知识产权(IP)的FPGA供应商。VectorPath™S7t-VG6加速卡使用了Achronix采用7nm 工艺打造的、结合了很多功能的Speedster®7t FPGA芯片,不仅可以在内部提供高吞吐量数据加速,而且还支持现今从机器学习到先进仪器等系统所需的高度分布式、网络化的架构。

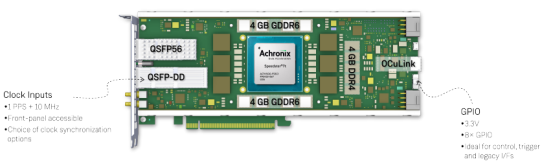

图1:VectorPath S7t-VG6加速卡

软件友好型的硬件提供了最大的灵活性

通过对分布式架构提供直接支持,VectorPath S7t-VG6加速卡中使用的Speedster7t FPGA芯片标志着与传统FPGA架构不同的重大转变,它使面向软件的开发人员更容易地构建定制化的处理单元。这种创新的全新架构与诸如英特尔(Intel)和赛灵思(Xilinx)等供应商生产的传统FPGA完全不同,传统FPGA的设计关注点并不在数据加速。

在设计Speedster7t的架构时,Achronix创建了一种可最大限度地提高系统吞吐量的FPGA芯片,同时还为计算机架构师和开发人员提高了易用性。与传统的FPGA架构相比,Speedster7t FPGA芯片的一个关键差异化点在于它包括一个创新的二维片上网络(2D NoC),可以在逻辑阵列内的处理单元与各种片上高速接口和存储器端口之间流传数据。

传统的FPGA要求用户去设计电路来将其加速器连接到高速以太网或PCIe数据端口和/或存储器端口。通常,一个独立系统是由连接到多个高速端口的多个加速器组成。例如,下图就说明了一种场景,其中有两个加速器连接到两个存储端口上,以共享一个存储空间。这种场景使用了FIFO来管理存储器和FPGA时钟之间的时钟域交叉(CDC)。此外,FPGA逻辑架构中还需要一个交换功能来管理寻址、仲裁和反压。在传统的FPGA中,这项功能会消耗大量的FPGA资源,并且其复杂程度足以降低系统性能并使时序收敛变得复杂。

Achronix采用了由软件设计来实现硬件的方法,而这种硬件中的以太网和其他高速I / O端口可用二维片上网络(2D NoC)轻松地连接到定制的加速器功能上。Speedster7t NoC不再需要设计CDC和交换功能来将加速器连接到高速数据或内存端口。通过简单地将这些功能连接到NoC,就消除了连接方面的难题,从而简化了设计,减少了FPGA资源的消耗,提高了性能并简化了时序收敛。

图2:传统FPGA设计面临的挑战

图3:Speedster7t二维片上网络支持软件友好型硬件

为了实现高性能的算术运算,每个Speedster7t器件都具有一个大型可编程计算单元阵列,它们被有序地放置在机器学习处理器(MLP)单元模块中。MLP是一个高度可配置的计算密集型单元模块,在每个周期内可支持多达32个乘法/累加(MAC)运算。在以加速器为中心的设计中,MLP的存在使得在完全可编程逻辑和硬连线算术单元之间能够有效地共享资源。

尽管有些FPGA倾向于使用HBM2存储器,其中FPGA和存储器被组装成一个昂贵的2.5D封装,而Speedster7t系列却采用GDDR6内存标准接口。这种接口提供了当今片外存储器可实现的最高性能,并且成本显著降低,从而使团队更容易去实现带有高带宽存储阵列的加速器。一个GDDR6存储控制器可以支持512 Gbps的带宽。VectorPath S7t-VG6加速卡可提供八组存储器,总存储带宽可以达到4 Tbps。此外,板上还有一个DDR4接口,可用于访问频率较低或不需要GDDR6吞吐量的数据。

VectorPath S7t-VG6加速卡提供了许多高性能接口,用来支持分布式架构和高速主机通信。现在,该加速卡提供了PCIe Gen 3.0的16通道合规性和认证,并提供获取Gen 4和Gen 5资质认证的途径。在以太网连接方面,该加速卡采用已获得广泛支持的光学接口模块,依据QSFP-DD和QSFP56标准,能够处理高达400 Gbps的超高线速。

在加速卡的另一端还有一个OCuLink扩展端口,以支持很多其他的低延迟应用场景。例如,OCuLink端口可用于将加速卡连接到各种外围设备上,比如用于计算存储或数据库加速应用的NVMe存储阵列。与采用连接到主处理器的PCIe接口相比,OCuLink连接能够成为一个更好的选择,因为它提供了一种消除了系统级延迟和抖动的高确定性的连接。OCuLink端口还可以引入其他网络连接,从而可扩展实现QSPF-DD或QSFP56之外的各种端口规格。

图4:VectorPath的网络和存储接口

在VectorPath S7t-VG6加速卡的前面板上还包括多个时钟输入,它们是在将多个加速卡同步到一起时通常需要的。两个SMB时钟输入连接器支持从1PPS和10 MHz的时钟输入,它们在进入FPGA之前,就已被连接到抖动清除器。一旦进入FPGA,这些时钟就可以被倍频或分频成为特定应用所需的频率。

还可以通过通用数字I / O端头进行进一步扩展。该I / O端口支持单端3.3V连接和低电压差分(LVDS)信号,支持外部时钟、触发器和专用I / O等自定义信号直接连接到Speedster7t FPGA。该扩展端口还可用于将VectorPath加速卡改造为传统硬件。

图5:VectorPath时钟输入和GPIO

适用于小批量和大批量需求

VectorPath S7t-VG6加速卡已考虑到了每个细节,例如可支持被动和主动空气散热和液体散热。此外,BittWare和Achronix还为医疗等需要更长产品生命周期的领域确保提供长期的供应与支持。在这些市场中,基于GPU的PCIe加速卡较短的产品生命周期与超过10年的系统服务支持需求是不符的。

对于更大批量需求,特别是在边缘计算等场景中,客户可以使用BittWare的成本降低计划来简化硬件,其设计仅仅支持客户所需的I / O选项。此外,BittWare也可提供电路板设计文件以及VectorPath S7t-VG6加速卡随附的软件和驱动器的使用。利用Achronix的Speedcore eFPGA IP,也可以走向定制系统级芯片(SoC)器件。客户可以构建自己其中包括Speedster7t可编程性的SoC,但又具有ASIC的成本结构。

为了实现更好的开发和更便捷的部署,VectorPath S7t-VG6加速卡可以由BittWare以其TeraBox平台的形式来提供预先集成的多核服务器。外形从2U到5U,TeraBox的机架式机箱最多可容纳16个BittWare PCIe加速卡,并由双路英特尔(Intel) Xeon处理器管理。作为一个完整的解决方案,TeraBox为客户提供了启动和运行FPGA开发的最快机制。在Bittworks II和FPGA Devkit软件的支持下,用户可以直接使用TeraBox并立即开始开发工作。或者,客户也可以从Dell和HP Enterprise购买包含BittWare加速卡的预配置服务器。

图6:TeraBox平台的部署