台积电在3nm制程工艺研发遇到瓶颈,3nm量产要“迟到”

2021-01-06

来源:镁客maker网

即便没有在2022年如期推出3nm量产,也是十分正常的事情。

在突破先进制程的道路上,身为芯片代工龙头的台积电从来不会吝惜在资金上的投入。

据台媒报道,台积电在2020年资本开支170亿美元,创下了历史新高,这其中绝大部分用于5nm的技术突破。

随着3nm风险试产在即,台积电在新一年的开支也将破新高。

但根据Digitimes的最新报道,台积电在3nm制程工艺的研发上遇到了关键技术的瓶颈,研发也不得不推迟。

推迟的3nm

早在去年4月,受到疫情的影响,EUV光刻机等关键设备在物流上受到延误,这也导致台积电在设备安装上迟迟无法按期完成,原计划在6月份风险试产的3nm FinFET工艺,延期到10月份。

相应的,台积电南科18厂原定于10月份安装设备的3nm生产线也被顺延一个季度,直到11月24日才正式开工,而量产则被延期到2022年。

目前尚不清楚台积电在3nm工艺研发过程中遇到的关键瓶颈具体指什么,但如果想顺利在2022年完成量产,台积电必须在技术上有所突破。

此前,台积电CEO魏哲家在财报分析师电话会议上曾透露,他们的3nm工艺仍将采用成熟的鳍式场效应晶体管技术(FinFET)。而作为竞争对手的三星在3nm工艺上将采用环绕栅极晶体管(GAAFET)技术。

尽管相比于N5(5nm),台积电N3的密度提高了50%,但工艺上依旧是FinFET,换句话说,这次的台积电太过于“保守”了。

这背后,是台积电意图兼顾成本与效能。毕竟从三星宣布的相关信息来看,3nm GAA技术的成本可能会超过5亿美元,且其制造工艺与传统的FinFET有一定的相似之处,但在技术要求和难度上更上一层台阶。

就FinFET技术本身,随着晶体管尺度向3nm 迈进,其尺寸已经去向缩小至极限。此时,无论是鳍片距离、短沟道效应、还是漏电和材料极限也使得晶体管制造变得岌岌可危,甚至物理结构都无法完成。

可以推测的是,台积电已经找到了可行的改进方案,只是目前遇上了瓶颈。

5nm工艺“翻车”?

有人说,手机SoC前几年井喷式的发展,主要是受益于芯片工艺以及散热技术的进步。伴随着技术和材料上的限制,手机SoC的瓶颈已经在5nm工艺上得到了体现。

随着小米11的正式发布,短短几个月里,苹果、华为、三星还有高通都相继发布了各自的5nm芯片。

但从各家媒体的评测来看,这几家公司的芯片都或多或少出现翻车的情况,实际性能提升并没有宣传中那么优秀。

以骁龙888为例,这款芯片采用三星5nm LPE制程工艺,在这款芯片发布之前,苹果A14和麒麟9000芯片都采用了台积电代工的5nm制程工艺。

爱否科技的评测显示,在3DMark压力测试中,首发搭载骁龙888的小米11一直提醒温度过高,导致测试无法进行。并且,在经过连续几次的测试后,机身表面温度达到了51度,而稳定性只有91%。这一问题在多家测评中均有出现。

针对小米11的翻车,有人把原因归结于测试机相对较老的固件以及Arm和高通的设计问题,但事实上除了三星代工的骁龙888以外,由台积电代工的5nm芯片同样表现不理想。

比如相比A13,A14的性能提升并不明显,而华为的麒麟9000芯片,功耗控制较之官方数据也存在较大差异。

单从测试结果来看,今年的5nm制程工艺,不管是台积电还是三星,实际表现都没能达到官方所宣传的效果。

仔细来看,台积电每隔两年就将密度提升1.8倍的速度相当激进,远高于业界水平,而三星同样在追赶台积电的道路上加快了脚步。

所以目前的台积电在3nm上依然十分激进,并且没有前人的经验,即便没有在022年如期推出3nm量产,也是十分正常的事情。

缺电,台积电最大的隐患

在解决完工艺上的问题后,“缺电”就成了台积电3nm道路上的最大威胁。

作为用电大户,台积电前几年的用电量就占据了全台湾用电量的5%以上。

根据台积电企业社会责任报告书,2016年台积电用电量就已高达88.53亿度,较2015年增加了11%。当时台积电仅在竹科的Fab耗电功率已经超过72万千瓦。到了2019年,台积电的耗电量猛增到143.3亿度。

在过去五年台湾增长的用电量中,有三分之一都被台积电占用,而这只是台湾地区庞大半导体企业中的一员。

按照原计划的3nm量产时间,2022年到2023年应备总供电容量增加近100万千瓦,2024年到2025年进一步大增257.6万千瓦,而这恰好与台积电3nm以及2nm量产时间相符合。

按照台积电的估算,台湾地区的备用电量远远无法满足台积电的需求。

台积电造的每一颗芯片需要经过近3000道工序才能完工,而这其中需要利用大量的半导体设备,并一直维持恒温、高压等各种复杂环境,这一切都需要电,芯片越多、制程越先进,用的电就越多。

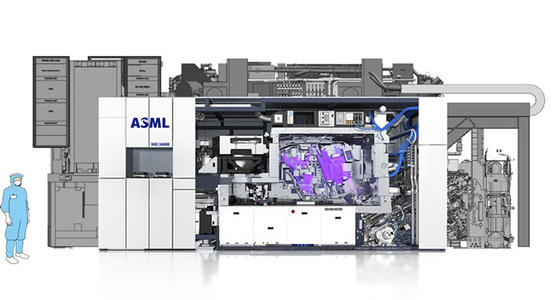

由于7nm以下的先进工艺制程必须要使用EUV光刻机,而一台EUV光刻机,一天耗电3万度。SK海力士此前就曾表示,“EUV的能源转换效率(wall plug efficiency)只有0.02%左右。”极紫外光本身的损耗过大,这也是造成转换率低的一大原因。

数据显示,EUV机台用电量占台积电公司能源使用50%以上,如果EUV机台数量逐年增加,那么台积电对于电能的消耗也将进一步快速增长。

早在2015年的时候,张忠谋就指出,困扰台积电发展的唯一要素就是缺电、停电,这一影响对于现阶段的台积电已经是不可估量的。如果后期的3nm、2nm工厂也出现停电情况,损失方面将会是5nm生产线的几倍。

结语

在目前的情况之下,无论是GAA还是FinFET,都存在技术上的瓶颈。除了台积电的3nm受限以外,无独有偶,三星的3nm似乎也不顺利,其晶圆工厂已经将进度调后。

图 | 三星公布的5nm成本

不过,业内人士对于“台积电2022年开始量产3nm工艺”还是充满信心。而要实现这一目标,除了解决技术上的难题以外,台积电还要从节省能源上下足功夫。