长江存储发布第四代闪存,200+时代已来临

2022-08-03

作者: 李寿鹏

来源:半导体行业观察

长江存储发布第四代闪存,第四代闪存性能如何?第四代闪有什么技术创新?

今日,国产闪存供应商在2022年闪存峰会(FMS)上宣布,公司正式推出了基于晶栈®3.0(Xtacking®3.0)技术的第四代TLC三维闪存X3-9070。据长江存储介绍,与上一代产品,新的X3-9070拥有更高的存储密度,更快的I/O速度,并采用6-plane设计。

首先在性能方面,据介绍,X3-9070实现高达2400MT/s的I/O传输速率,符合ONFI5.0规范,这相较于长江存储上一代产品实现了50%的性能提升;再看密度方面,得益于晶栈?3.0的架构创新,X3-9070成为了长江存储历史上密度最高的闪存颗粒产品,能够在更小的单颗芯片中实现1Tb的存储容量;最后,得益于创新的 6-plane设计,X3-9070相比传统4-plane,性能提升50%以上,同时功耗降低25%,能效比显著提升,可为终端用户带来更具吸引力的总体拥有成本(TCO)。

按照长江存储执行副总裁陈轶所说,X3-9070闪存颗粒是长江存储近年来在三维闪存领域的匠心之作,它拥有出色的性能表现和极高的存储密度,能够快速高效地应用于主流商用场景之中。

“面对蓬勃发展的5G、云计算、物联网、自动驾驶、人工智能等新技术带来的全新需求和挑战,长江存储将始终以晶栈?为基点,不断开发更多高品质闪存产品,协同上下游存储合作伙伴,用晶栈?为存储产业赋能,践行‘成为存储技术的领先者,全球半导体产业的核心价值贡献者’的使命和责任。”陈轶强调。

缩小和国际巨头的技术差距

作为一家成立刚满六年的公司,长江存储的发展绝对称得上“神速”,公司也在这短短几年间,缩短了公司和国际领先巨头的差距,这从长江存储上述的介绍中可见端倪。

有关注半导体行业观察最近文章的读者应该对6-plane设计、ONFI5.0规范和2400MT/s的I/O速度这些数字似曾相识,因为在上个礼拜题为《闪存,正式进入232层时代》的文章里,我们在介绍美光打造的全球首款232层NAND Flash的时候,就讲到美光在其最新产品上采用了相关技术。

也正是在这些技术的支持下,让长江存储的产品获得了不错的性能表现。

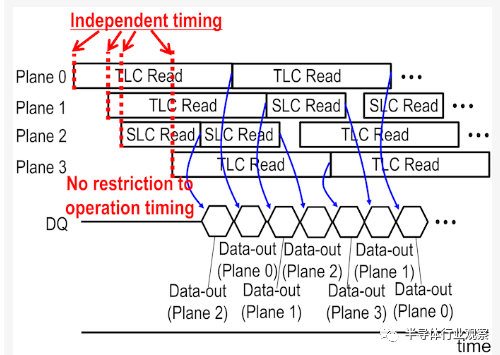

先看“6-plane设计”。在上文谈到的“232层闪存”的文章中,我们有简单披露了这个设计给闪存带来的好处。但其实在美光和长江存储跨入这个设计之前,行业的主流是使用“4-plane设计”。

按照anadtech报道,将 NAND 闪存die分为四个平面允许die并行处理更多操作,但不会使其表现得非常像四个独立的die,这样做也使其并行执行的操作存在限制:例如,同时写入仍然必须转到每个平面(plane)内的同一字线。但随着闪存die中平面数量的增加,制造商一直在努力放松其中的一些限制。从几年前开始,制造商已经引入了独立的multi-plane读取,这意味着不同平面中的同时读取对每个平面内正在读取的位置没有任何限制——这是随机读取吞吐量的一大胜利。

anadtech的报道进一步指出,现在,对multi-plane操作的另一个限制正在放宽:不同平面的读取操作的时序不需要排队。这使得一个平面可以从 SLC 页面( pages)执行多个读取,而另一个平面正在从 TLC 或 QLC 页面执行单个较慢的读取。此功能称为异步独立(多)平面读取( Asynchronous Independent (Multi-)Plane Read)。

这样做的实际效果是,对于读取操作,一个大型 4 平面die现在可以匹配四个较小的 1 平面die的性能。这减轻了更高的每裸片容量给每个通道只有一个或两个裸片的 SSD 带来的许多性能劣势。

从这个关于plane的介绍中我们可以看到,长江存储这个增加plane的意义。

再看ONFI(Open NAND Flash Interface的缩写)标准。据了解,这是由英特尔,美光,海力士,台湾群联电子,SanDisk, 索尼,飞索半导体为首宣布统一制定的连接NAND闪存和控制芯片的接口标准,当初制定ONFI标准的主要目的是统一当时混乱的闪存标准。ONFI 方面也表示,其存在是致力于通过标准化 NAND 闪存接口来解决主机系统必须适应供应商设备等问题,减少供应商和代际不兼容并加速新 NAND 产品的采用,ONFI 5.0则是该标准的最新版本。

资料显示,ONFI 5.0于 2021 年 5 月发布,能将 NV-DDR3 I/O 速度扩展至 2400MT/s。引入了速度高达 2400MT/s 的新型 NV-LPDDR4 低功耗接口。使用 NV-LPDDR4 接口,则定义了可选的数据总线反转 (DBI) 功能。此外,新标准还添加了新的更小尺寸 BGA-178b、BGA-154b 和 BGA-146b 封装规范。

通过上述介绍以及对比早前DigiTimes“传长江存储将跳过原定192层技术,直接挑战232层NAND”的报道,我们可以初步认为长江存储的新一代闪存是232层的设计。从当前的时间节点看来,长江存储的这次发布仅落后于美光,成为全球第二家跨入200层的闪存企业,缩短了与国际巨头的差距。

虽然取得了进步,但是我们也必须承认,我们和国际领先巨头还存在明显的差距。例如长江存储在介绍中表示,公司可以再单颗芯片中实现1Tb的存储容量。对比美光的描述,他们能够在单颗芯片中实现2Tb的存储容量。此外,按照长江存储的说法,公司目前只是发布了产品,在笔者看来,这大概率是处于送样阶段。但按照美光的说法,他们已经应该量产了,这中间的差距也是显而易见的。

Xtacking®3.0:长江存储的利剑

在长江存储的闪存技术“武器库”中,晶栈Xtacking®是他们当之无愧的首要依仗。

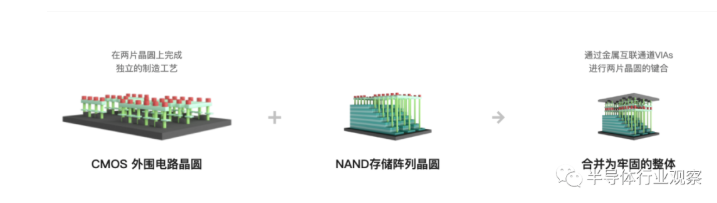

据官方资料介绍,在晶栈Xtacking® 架构推出前,市场上的3D NAND主要分为传统并列式架构和CuA(CMOS under Array)架构。而长江存储通过创新布局和缜密验证,经过长达8年在3D IC领域的技术积累和3年的研发验证后,终于将晶圆键合这一关键技术在3D NAND闪存上得以实现。

长江存储表示,晶栈Xtacking® 可实现在两片独立的晶圆上加工外围电路和存储单元,这样有利于选择更先进的逻辑工艺,从而让NAND获取更高的I/O接口速度及更多的操作功能。当两片晶圆各自完工后,创新的晶栈Xtacking® 技术只需一个处理步骤即可通过数十亿根垂直互联通道(VIA)将两片晶圆键合,合二为一。值得一提的是,这样的设计却拥有了与同一片晶圆上加工无异的优质可靠性表现,这项技术为未来3D NAND带来更多的技术优势和无限的发展可能。

长江存储进一步指出,在传统3D NAND架构中,外围电路约占芯片面积20~30%,但晶栈 Xtacking® 技术创新的将外围电路置于存储单元之上,从而实现比传统3D NAND更高的存储密度,芯片面积可减少约25%。“晶栈Xtacking® 技术充分利用存储单元和外围电路的独立加工优势,实现了并行的、模块化的产品设计及制造,产品开发时间可缩短三个月,生产周期可缩短20%。此外,这种模块化的方式也为引入NAND外围电路的创新功能以实现NAND闪存的定制化提供了可能。”长江存储方面强调。

按照长江存储的说法,随着层数的不断增高,公司基于晶栈Xtacking® 所研发制造的3D NAND闪存将更具成本和创新优势。而自在长江存储64层产品上首次亮相以来,Xtacking架构迄今已经进行了三代更新。

记得在2018年推出第一代Xtacking®技术产品的时候,当时大多数NAND供应商仅能供应1.0Gbps或更低的速度,但基于Xtacking®技术打造的闪存能有望将NAND的I/O速度提升到3.0Gbps,将其速度提高到主流速度的三倍。

2019年,长江存储又宣布在公司的第三代3D NAND闪存中应用Xtacking® 2.0架构。

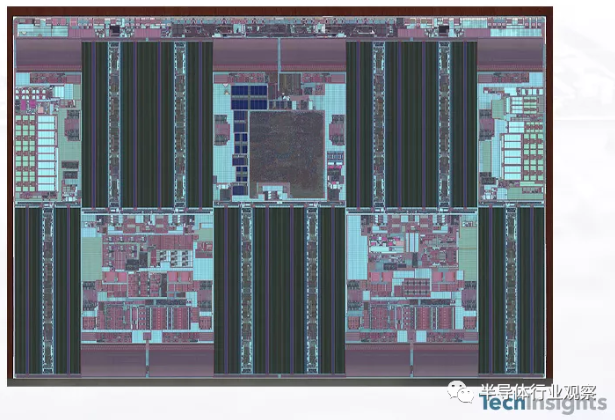

据知名分析机构Tech Insights在2021年发布的拆解对比显示,与使用 Xtacking® 1.0(4.42 Gb/mm?、256 Gb)制造的裸片相比,长江存储在Xtacking® 2.0上实现了 92% 的位密度(8.48 Gb/mm?、512 Gb)提升,这表明长江存储对该技术的路线图制定了稳健的未来计划。Tech Insights进一步指出,令人惊讶的是,长江存储凭借其 TLC Xtacking 2.0 NAND 实现了比三星(6.91)、美光(7.76)和 Sk hynix(8.13)更高的密度水平(8.48)

到了Xtacking® 3.0时代,按照长江存储的说法,公司该架构的存储密度又获得了进一步的提升,这也使X3-9070成为了长江存储历史上密度最高的闪存颗粒产品。

写在最后

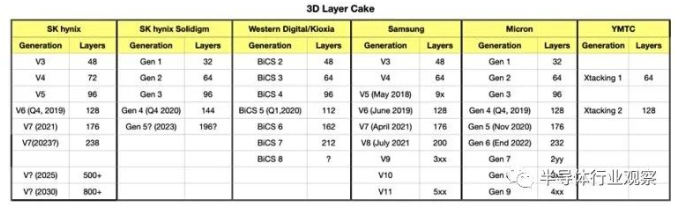

存储巨头在过去几十年的推进过程中,都分别都拥有了其独当一面的技术和核心竞争力和层数规划。如下图所示,SK海力士、三星和美光甚至都将3D闪存规划到500层,甚至800层以后,在这种情况下,一个合理的架构,就成为了闪存厂商持续推进层数堆叠的底气。

凭借着后发优势,长江存储的Xtacking® 已经在市场上获得了高度认可。但对于他们来说,未来的发展依然存在很多挑战。

正如IEEE在其报道中所说,除了添加越来越多的层外,NAND 闪存制造商还通过将多个位(bits)封装到单个设备中来提高存储位的密度。例如美光芯片的每个存储单元都能够每个单元存储三位。也就是说,存储在每个单元中的电荷会产生足够明显的效果来辨别八种不同的状态。

IEEE进一步指出,虽然 3 位/单元产品(称为 TLC)占大多数,但也有4 位产品(称为 QLC)。今年早些时候,西部数据研究人员在IEEE 国际固态电路会议上展示的一款 QLC 芯片更是在 162 层芯片中实现了15 Gb/mm?的密度。铠侠工程师上个月在IEEE VLSI技术和电路研讨会上甚至还展示了一个 7 位单元,但它需要将芯片浸入 77 开尔文液氮中。

由此可见,对于长江存储来说,长路漫漫。特别是在当前地缘政治带来的更多不确定性影响下,他们还需要投入更多以进行求索。

更多信息可以来这里获取==>>电子技术应用-AET<<