祝贺!本刊编委尹首一教授在ISSCC 2023发表3篇论文

2023-03-10

来源:清华大学集成电路学院

2月19日至23日,第70届ISSCC(国际固态电路会议)在美国旧金山召开,清华大学集成电路学院作为第一署名单位在ISSCC 2023发表了8篇学术论文,所涉及研究内容包括存内计算视觉芯片、量子计算芯片、多模态Transform芯片、异步类脑芯片、可重构存内张量计算芯片、超宽带收发机、分频器、振荡器等。

本刊编辑委员会专家尹首一教授作为通讯作者的3篇文章获得发表,下面我们对相关论文进行介绍。

ISSCC (International Solid-State Circuits Conference)国际固态电路会议始于1953年,是全球学术界和工业界公认的集成电路设计领域最高级别会议,被认为是“集成电路设计领域的奥林匹克大会”。ISSCC通常是各个时期国际上最尖端固态电路技术最先发表之地。每年吸引超过3000名来自世界各地工业界和学术界的参会者。

存内计算视觉芯片CV-CIM

代价匹配算法需要精确计算图像间的相似度,已经被广泛应用于自动驾驶,机器人,AR/VR等领域,但由于其频繁的数据访存,导致其难以应用于低功耗场景中。集成电路学院魏少军、尹首一教授团队提出了采用存算一体范式的CV-CIM,将计算单元与SRAM存储单元完成合并,减少数据搬移。利用异或逻辑的自反性,结合律等,可重构为乘法,加法,减法,比较等多种基本算子。进一步经过数模混合存算单元的配合,实现包括L0/L1/L2在内的多种距离计算算法;并利用图像相似度,动态扩充计算数据稀疏度,扩展计算噪声容限,提升计算精度;通过增加行方向细粒度地址控制,列方向读写并行模式,大幅提升存算系统的利用率。考虑到模拟单元受PVT影响,增加Canary BIST单元保证计算系统鲁棒性。CV-CIM作为国际首款针对图像匹配的存算一体芯片,在28nm工艺上成功实现流片,峰值能效为1158TOPs/W,面积为0.387mm^2。

该工作以 “CV-CIM: A 28nm XOR-derived Similarity-aware Computation-In-Memory For Cost Volume Construction”为题发表在ISSCC2023。集成电路学院博士研究生岳志恒为论文第一作者,尹首一教授为通讯作者。

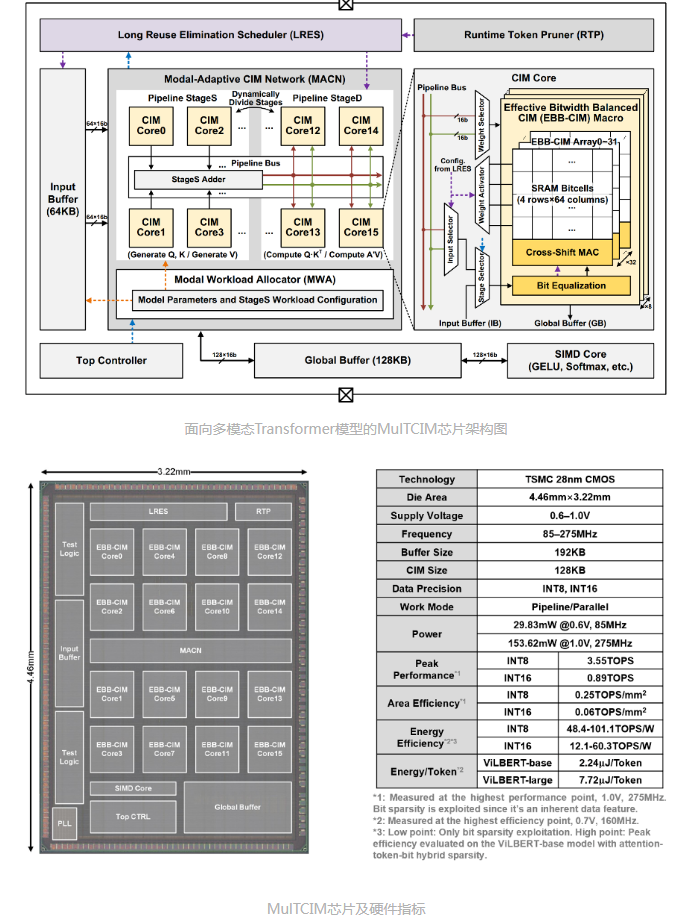

多模态Transform芯片

多模态Transformer是当下最流行的处理多种模态信号(视觉、文字、语音等)的AI模型之一,已广泛应用于视频问答、多语言图像检索等任务中。这类模型巨大的计算量、频繁的数据访问、独特的跨模态注意力机制对AI芯片设计造成诸多挑战。集成电路学院魏少军、尹首一教授团队提出国际首款基于可重构数字存算一体架构的多模态Transformer AI芯片MulTCIM。研究团队充分利用跨模态注意力机制中的计算冗余性,设计出综合利用attention-token-bit三个层次混合稀疏性的存算一体架构:1)使用注意力局部性调度器优化attention稀疏,提高存算单元利用率;2)采用模态自适应存算一体网络优化token稀疏,减少跨模态切换时的等待时间;3)利用位宽均衡存算一体单元优化bit稀疏,降低存算一体单元的计算延迟。MulTCIM芯片使用TSMC 28nm工艺成功流片,在典型多模态Transformer模型ViLBERT上仅产生2.24μJ/Token的能耗,相比于ISSCC2022上发表的Transformer芯片可获得5.91倍的能效提升。

该工作以“MulTCIM: A 28nm 2.24μJ/Token Attention-Token-Bit Hybrid Sparse Digital CIM-based Accelerator for Multimodal Transformers”为题发表在ISSCC2023。集成电路学院毕业生涂锋斌博士为论文第一作者,尹首一教授为论文通讯作者。

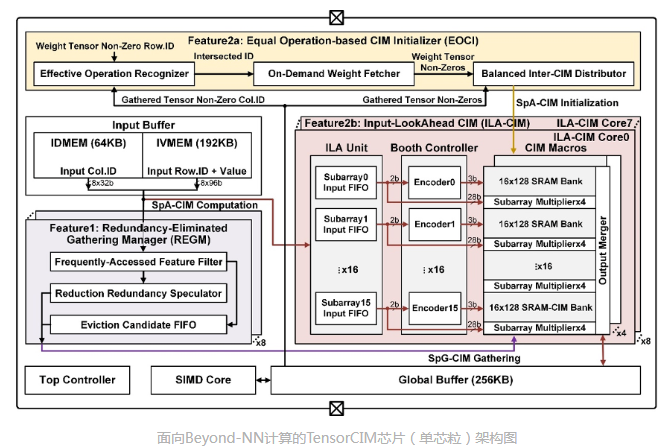

可重构存内张量计算芯片TensorCIM

Beyond-NN计算是面向通用智能场景的新型计算类型。不同于传统的处理图像、语音等规则数据结构的神经网络,Beyond-NN计算需要处理真实世界中的非规则数据结构,例如社交网络、知识图谱、推荐系统等。针对Beyond-NN在算力、访存、功能三方面的技术挑战,集成电路学院魏少军、尹首一教授团队提出国际首款基于可重构数字存算一体架构的多芯粒张量处理器TensorCIM:1)TensorCIM采用多芯粒系统对算力和存储容量进行扩展,在降低制造成本的同时,为不同规模的Beyond-NN场景提供可扩展的系统解决方案。2)TensorCIM通过数字存算一体架构大幅减少数据搬运,并支持高精度的浮点计算以保证准确度。3)TensorCIM将可重构技术与数字存算一体相结合,实现稀疏张量聚集和稀疏神经网络计算两种模式的动态切换,保持极高的计算资源利用率。TensorCIM芯片使用TSMC 28nm工艺成功流片,在图神经网络、推荐系统等典型Beyond-NN应用上验证,取得3.7nJ/Gather的稀疏张量聚集效率和8.3TFLOPS/W的稀疏FP32张量代数能效,相比同期浮点存算一体AI芯片能效提升5.6倍。

该工作以“TensorCIM: A 28nm 3.7nJ/Gather and 8.3TFLOPS/W FP32 Digital-CIM Tensor Processor for MCM-CIM-Based Beyond-NN Acceleration”为题发表在ISSCC2023。集成电路学院毕业生涂锋斌博士为论文第一作者,尹首一教授为论文通讯作者。