消息称SK 海力士五层堆叠3D DRAM内存良率已达56.1%

2024-06-24

来源:IT之家

6 月 24 日消息,韩媒 BusinessKorea 报道,业内人士透露 SK 海力士在 6 月 16 至 20 日在美国夏威夷举行的 VLSI 2024 峰会上发表了有关 3D DRAM 技术的最新研究论文。

在这篇论文中,SK 海力士报告其五层堆叠的 3D DRAM 内存良率已达 56.1%,实验中的 3D DRAM 展现出与目前 2D DRAM 相似的特性。

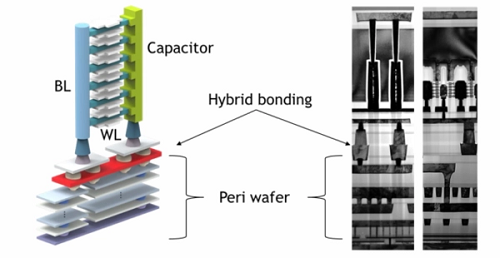

据介绍,与传统的 DRAM 水平排列内存单元不同,3D DRAM 垂直堆叠单元,可以在相同空间内实现更高的密度。

不过,SK 海力士指出,与 2D DRAM 的稳定运行不同,3D DRAM 表现出不稳定的性能特征,需要堆叠 32 到 192 层存储单元才能实现普遍应用。

三星正在开发 16 层堆叠 3D DRAM,并在今年 3 月的 MemCon 2024 展会上宣布计划在 2030 年左右实现 3D DRAM 产品商业化应用。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。