Turbo简化译码算法的FPGA设计与实现

2008-04-21

作者:赵旦峰, 雷李云, 杨建华

摘 要: 在深入分析Turbo译码算法" title="译码算法">译码算法的基础上,采用MAX-LOG-MAP" title="MAX-LOG-MAP">MAX-LOG-MAP算法进行了Turbo码译码器" title="译码器">译码器的FPGA设计与实现,并给出相应实现参数和结构。对FPGA的实现与MATLAB浮点算法做了仿真比较。

关键词: Turbo码 MAX-LOG-MAP算法 FPGA

Turbo码自1993年提出以来[1],由于其接近香农极限的优异译码性能,一直成为编码界研究的热点。近年来,用户对通信质量的要求越来越高,学者们已将研究重点从理论分析转移到Turbo码的实用化上来。Turbo码现已成为深空通信的标准,即第三代移动通信(3G)信道编码方案[2]。

Turbo码虽然具有优异的译码性能,但是由于其译码复杂度高,译码延时大等问题,严重制约了Turbo码在高速通信系统中的应用。因此,如何设计一个简单有效的译码器是目前Turbo码实用化研究的重点。本文主要介绍了短帧Turbo译码器的FPGA实现,并对相关参数和译码结构进行了描述。

1 几种译码算法比较

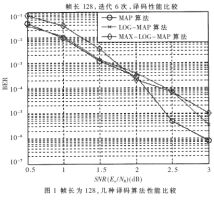

Turbo码常见的几种译码算法中,MAP算法[1][3]具有最优的译码性能。但因其运算过程中有较多的乘法和指数运算,硬件实现" title="硬件实现">硬件实现很困难。简化的MAP译码算法是LOG-MAP算法和MAX-LOG-MAP算法,它们将大量的乘法和指数运算转化成了加减、比较运算,大幅度降低了译码的复杂度,便于硬件实现。简化算法中,LOG-MAP算法性能最接近MAP算法,MAX-LOG-MAP算法次之,但由于LOG-MAP算法后面的修正项需要一个查找表,增加了存储器的使用。所以,大多数硬件实现时,在满足系统性能要求的情况下,MAX-LOG-MAP算法是硬件实现的首选。通过仿真发现,采用3GPP的编码和交织方案[2],在短帧情况下,MAX-LOG-MAP算法同样具有较好的译码性能。

如图1所示,帧长为128,迭代6次,BER=10-5的数量级时, MAX-LOG-MAP算法的译码性能比MAP算法差大约0.6dB,比LOG-MAP算法差0.2dB左右。所以,本文采用3GPP的交织和(13,15)编码方案,MAX-LOG-MAP译码算法进行短帧Turbo码译码器的FPGA实现与设计。

2 MAX-LOG-MAP算法

为对MAP算法进行简化,通常将运算转换到对数域上进行,避免了MAP算法中的指数运算,同时,乘法运算变成了加法运算,而加法运算用雅可比公式简化成MAX*运算[4]。

将运算转化到正对数域进行运算,则MAX*可等效为:

按照简化公式(3)对MAP译码算法[1][3]的分支转移度量、前向递推项、后向递推项及译码软输出进行简化。

分支转移度量:

为防止迭代过程中数据溢出,对前后向递推项(5)、(6)式进行归一化处理:

3 FPGA实现关键技术

3.1 数据量化

在通信系统中,译码器的接收数据并不是连续不变的模拟量,而是经过量化后的数字量。接收数据的量化会引入量化噪声,从而影响译码的性能。所以,接收数据量化的精度直接影响到译码的性能。由参考文献[5~6]可知,采用3位量化精度就能得到与没有经过量化的浮点数据相近的译码性能。为了简化FPGA的设计,本文采用了统一的定点量化标准F(9,3),即最高位为符号位,整数部分8位,小数部分3位。由此,前后递推项(9)、(10)式的初始值可表示为:

3.2 MAX*运算单元

由前面的MAX-LOG-MAP算法介绍可知,MAX*运算单元是整个译码的主要运算单元,它与viterbi译码的ACS(加比选)运算单元一样,先分别进行加法操作,然后对所得结果进行比较,最后将较小的一个结果作为运算结果输出。实现结构如图2所示。

3.3 前后向递推运算单元

由公式(5)~(8)可知,前后向递推单元除了需要进行MAX*与运算外,还需要进行归一化处理。为得到较快的运算速度,首先,计算上一时刻所有状态的最小值,然后对当前时刻的每一状态进行MAX*运算,并将运算结果减去上一时刻的最小状态值" title="状态值">状态值,即得到当前时刻递推各状态的归一化值。实现结构如图3所示。

3.4 8状态值最小值运算单元

由MAX-LOG-MAP算法可知,在进行前后向递推归一化处理和计算译码软输出时,均需要计算每一时刻8个状态的最小值。为了减小计算延时,采用了8状态值并行比较的结构,与串行的8状态值比较结构相比较,要少4级延时。实现结构如图4所示。

4 仿真结果

按照以上所分析的简化译码算法、FPGA实现的相关参数和结构,整个译码采用Verilog HDL语言编程,以Xilinx ISE 7.1i、Modelsim SE 6.0为开发环境,选定Virtex4芯片xc4vlx40-12ff668进行设计与实现。整个译码器占用逻辑资源如表1所示。

MAX-LOG-MAP译码算法,帧长为128,迭代4次的情况下,MATLAB浮点算法和FPGA定点实现的译码性能比较如图5所示。

由MAX-LOG-MAP算法的MATLAB浮点与FPGA定点的性能比较仿真结果可知,采用F(9,3)的定点量化标准,FPGA定点实现译码性能和理论的浮点仿真性能基本相近,并具有较好的译码性能。

综上所述,在短帧情况下,MAX-LOG-MAP算法具有较好的译码性能,相对于MAP,LOG-MAP算法具有最低的硬件实现复杂度,并且Turbo码译码延时也较小。所以,在特定的短帧通信系统中,如果采用Turbo码作为信道编码方案,MAX-LOG-MAP译码算法是硬件实现的最佳选择。

参考文献

[1] BERRON C, GLAVICUS A, THITIMAAJSHIMA P. Near shannon limit error-correcting coding and decoding: Turbocodes(1) [C]. ICC’93,1993:1064-1074.

[2] 3GPP TS 25.212 Release6. Multiplexing and channel coding (FDD) [S], 2005.

[3] 王新梅,肖国镇.纠错码—原理与方法[M].西安:西安电子科技大学出版社,2001.

[4] ROBERTSON P, VILLEBRUN E, HOELER P. A comparison of optimal and sub-optimal MAP decoding algorithms operating in the log domain [C]. ICC.1995,1995:1009-1013.

[5] MONTORSI G, BENEDETTO S. Design of fixed-point iterative decoders for concatenated codes with interleavers. IEEE Journal on Selected Areas in Communications,2001:871-882.

[6] WU Yu Fei, WOERNER B D, BLANKENSHIP T K. Data width requirements in SISO decoding with module normalization. IEEE Trans. On Commun, 2001,(49)11.