Mentor推硬件加速仿真APP 提升设计效率

2016-03-22

作者:杨庆广

来源:电子技术应用

一般情况下硬件电路设计,在仿真的时候大多是采用软件仿真方式,这种方式在硬件电路相对简单的过去还可以满足电子工程师的需求。而在硬件电路日趋复杂的现在已经越来越难以满足实际设计需求。为此,硬件加速仿真的推出就必不可少。在硬件加速仿真领域Mentor Graphics有着丰富的经验,已经把硬件仿真推进到了第四个阶段——应用程序阶段。在该阶段中,单个硬件不再是区分因素,在硬件和操作系统上运行的应用程序将仿真平台转换成验证中心来工作,应用程序驱动使用新模型来减少SoC验证任务从而为硬件仿真加速。

硬件仿真发展的四个阶段

Veloce2 是Mentor公司的硬件仿真平台,目前运行Veloce OS3 操作系统,可针对当今复杂的片上系统 (SoC) 设计实现完整的功能验证。其自定义片上硬件仿真技术可提供高可靠的编译、类软件仿真似的交互式调试、超高的吞吐率以及快速验证收敛时间。

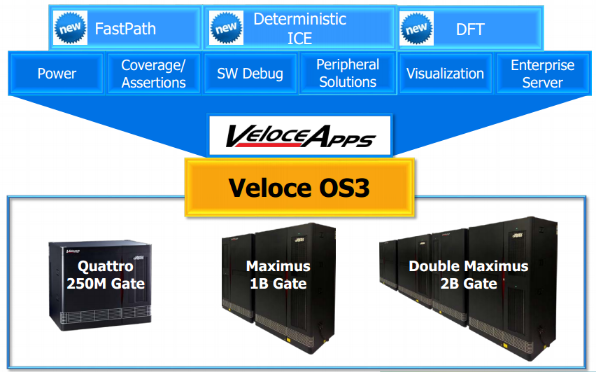

为了进一步提升硬件仿真效率,Mentor近期还推出了用于 Veloce®硬件仿真平台的新型应用程序(APP),包括 Veloce Deterministic ICE、 Veloce DFT 和 Veloce FastPath,可以解决复杂 SoC 和系统设计中的关键系统级验证难题。相比以硬件为中心的策略, Veloce OS3 上的 Veloce Apps 组合使用可以更快速地向更多工程师提供更丰富的功能。

Mentor APP架构图

Mentor推出的三个APP,可以说是在硬件仿真领域划时代的进步。这对于提升硬件仿真平台灵活度和效率有着至关重要的作用。每种新型 Veloce Apps 均可解决一项特定验证问题。

其中,Veloce Deterministic ICE 在调试过程中加入了 100%可见性和可重复性,从而克服了电路内仿真 (ICE) 环境的不可预知性,并可使用其他“ 基于虚拟的” 使用模型;· Veloce DFT 可提升流片之前的可测试性设计 (DFT) 验证速度,从而最大程度地降低了灾难性故障的风险,并极大减少了 DFT 插入后验证设计的运行时间;Veloce FastPath 在验证使用更快速的模型的多时钟域的 SoC 设计中优化硬件仿真性能。

除了这些已经推出的新型 Veloce Apps之外,Mentor还将继续扩充 Veloce Apps 库,以进一步提升硬件仿真效率。

这些新型Veloce Apps的推出,也是和Mentor优秀的Veloce OS 操作系统密不可分的。Veloce OS 操作系统为Veloce 平台增加了软件可编程性和资源管理。最新升级的 Veloce OS3 涵盖多项创新:集成全新的高性能计算平台,削减 50% 的编译时间。“即插即用”的门电路级处理设置,能接受平面或层次化设计。此流程可减少编译所需的内存量,从而提高性能。新的流程可以更加轻松地加载和验证门级设计,提高硅保真的可信度。硬件仿真和软件操作系统的时间能见度和时间波形调试与以前相比快2倍,结合了从运行时间到调试周期的软件和硬件改进,实现了更快可见性时间。