中文引用格式: 方胜利,孙航,李炜,等. Virtuoso Schematic Migration在模拟电路迁移中的应用[J]. 电子技术应用,2025,51(8):11-15.

英文引用格式: Fang Shengli,Sun Hang,Li Wei,et al. Application of VSM in analog circuit migration[J]. Application of Electronic Technique,2025,51(8):11-15.

引言

在现代电子设计领域,原理图是硬件开发的基石,它不仅是电路设计的蓝图,更是连接概念与实物的桥梁。然而,随着技术迭代加速、工具链演进和行业需求变化,原理图迁移逐渐成为工程师与设计团队无法回避的关键任务。这一过程涉及将现有电路设计从旧版EDA(电子设计自动化)工具或环境迁移至新平台,其复杂性远超简单的格式转换,而是涵盖数据兼容性、设计完整性、团队协作和长期战略价值的综合工程[1]。在EDA领域,原理图迁移是设计团队在工具升级、技术迭代或协作需求下不可避免的关键环节。随着半导体工艺进步、设计复杂度提升以及行业标准演进,传统的EDA工具可能无法满足现代设计需求,促使企业将旧版原理图迁移至更先进的平台。然而,这一过程并非简单的文件格式转换,而是涉及符号库匹配、网络连接验证、设计规则适配等一系列技术挑战,稍有不慎便可能导致设计功能变异、生产延误甚至成本超支[2]。

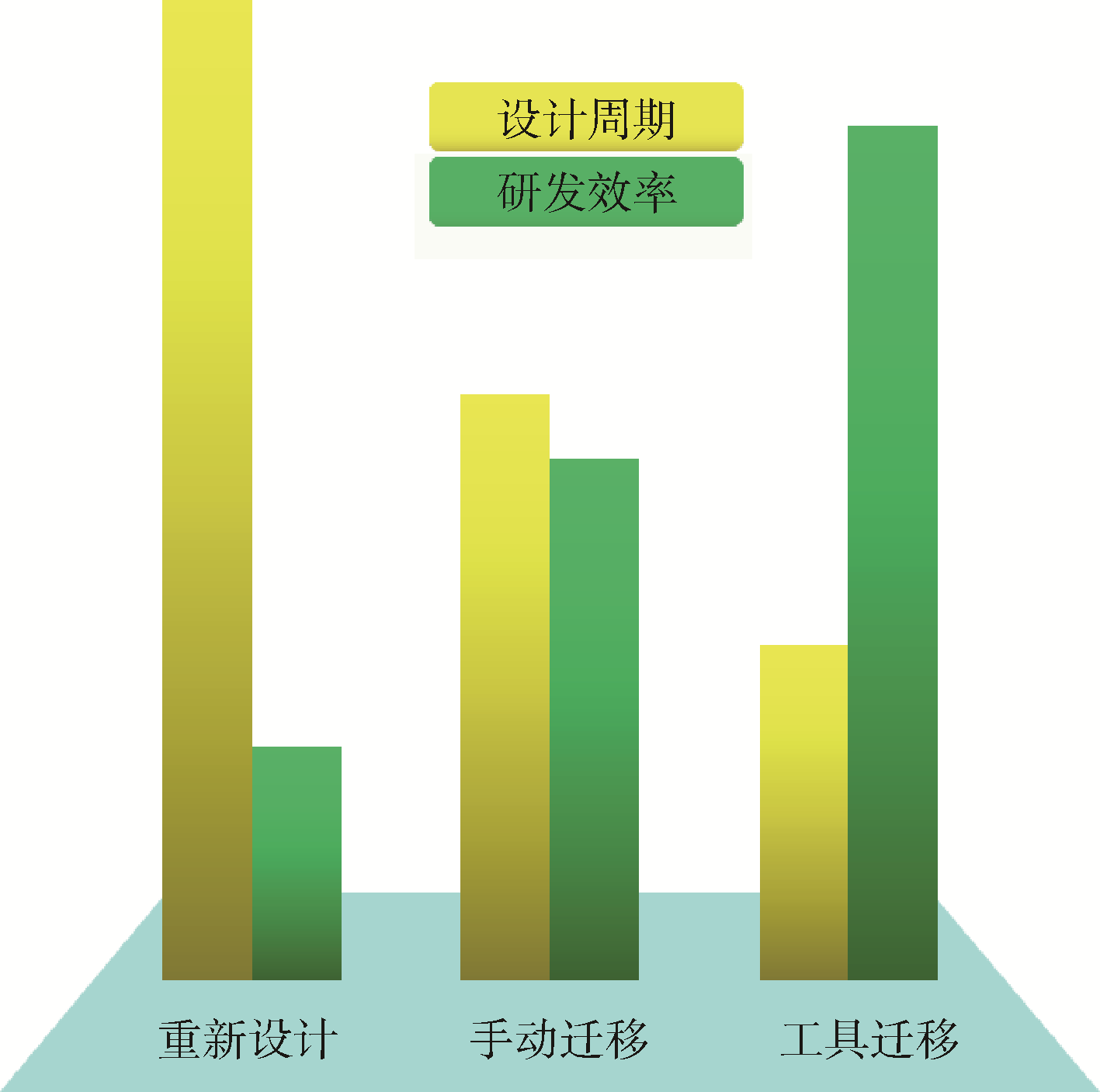

原理图迁移在芯片设计中变得越来越重要。如图1所示,首先,原理图迁移可以缩短设计周期,加速上市时间。迁移时可重用原有电路的架构、IP核和成熟模块,减少重新设计的时间。已有功能逻辑和测试用例可直接适配,减少验证和调试周期。现代EDA工具支持自动化迁移(如工艺库替换、布局优化),提升效率。其次,降低开发成本与风险减少研发投入。相比从零设计,迁移节省人力、流片和验证成本。原有电路已通过市场验证,工艺迁移主要解决物理实现问题,而非功能缺陷。避免全新设计可能存在的架构缺陷或性能不达预期的问题。优势在于快速响应工艺升级或供应链需求,但需注意模拟电路的敏感特性(如匹配、寄生效应),通常需人工干预优化。此外,当前原理图迁移仍然存在一些需要逐步攻克的难题。例如,如何确保迁移前后的器件参数一致,如何确保porting前后器件symbol尺寸不同时能够连线正确等问题。

尽管存在困难,成功的原理图迁移能显著提升设计效率、降低长期维护成本,并确保知识资产的可持续利用。近期Cadence在Virtuoso Studio IC23.1中基于Schematic XL开发出先进的电路迁移平台Virtuoso Schematic Migration(VSM),该工具不仅支持多个library之前的协同迁移,同时也支持电路顶层的hierarchy迁移,在不同晶圆厂商工艺间迁移时也能自动解决器件pin错位的问题。此外,Cadence近期推出的device mapping GUI将之前繁杂的mapping规则手动编写改成了用户界面点击的方式,大幅提高了mapping file 的准确性,同时也大幅提升了整个迁移流程的效率。综上,前端工程师可以利用migration实现更多工作,大幅度提高工作效率,缩短项目交付周期。

本文针对本公司一些实际的电路,基于该工具实现了在不同工艺间的迁移,大大提高了相同电路不同工艺间的复用效率,很大程度节省电路设计工程师对电路手动迁移所花费的时间。综上,工程师可以利用VSM来加速提高工作效率,缩短项目交付周期。

图1 原理图迁移中涉及周期和研发效率的对比关系

本文详细内容请下载:

https://www.chinaaet.com/resource/share/2000006621

作者信息:

方胜利1,孙航1,李炜1,丁学伟1,凌秋婵2

(1.深圳市中兴微电子技术有限公司,广东 深圳 518055;

2.楷登电子科技有限公司,上海 200120)